# Unidirectional Measurement Current-Shunt Monitor with Dual Comparators

#### **FEATURES**

- COMPLETE CURRENT SENSE SOLUTION

- DUAL COMPARATORS:

- Comparator 1 with Latch

- Comparator 2 with Optional Delay

- COMMON-MODE RANGE: -16V to +80V

- HIGH ACCURACY: 3.5% (max) Over Temperature

- BANDWIDTH: 500kHz

- QUIESCENT CURRENT: 1.8mA

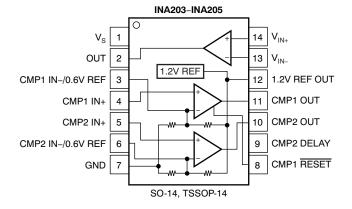

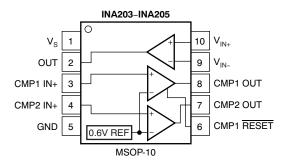

- PACKAGES: SO-14, TSSOP-14, MSOP-10

#### **APPLICATIONS**

- NOTEBOOK COMPUTERS

- CELL PHONES

- TELECOM EQUIPMENT

- AUTOMOTIVE

- POWER MANAGEMENT

- BATTERY CHARGERS

- WELDING EQUIPMENT

#### DESCRIPTION

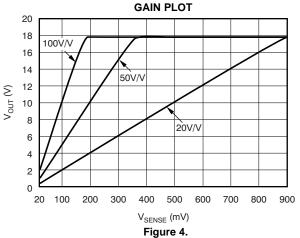

The INA203, INA204, and INA205 are a family of unidirectional current-shunt monitors with voltage output, dual comparators, and voltage reference. The INA203, INA204, and INA205 can sense drops across shunts at common-mode voltages from -16V to +80V. The INA203, INA204, and INA205 are available with three output voltage scales: 20V/V, 50V/V, and 100V/V, with up to 500kHz bandwidth.

The INA203, INA204, and INA205 also incorporate two open-drain comparators with internal 0.6V references. On 14-pin versions, the comparator references can be overridden by external inputs. Comparator 1 includes a latching capability, and Comparator 2 has a user-programmable delay. 14-pin versions also provide a 1.2V reference output.

The INA203, INA204, and INA205 operate from a single +2.7V to +18V supply. They are specified over the extended operating temperature range of -40°C to +125°C.

| DEVICE | GAIN   |

|--------|--------|

| INA203 | 20V/V  |

| INA204 | 50V/V  |

| INA205 | 100V/V |

#### **RELATED PRODUCTS**

| FEATURES                                                          | PRODUCT       |

|-------------------------------------------------------------------|---------------|

| Variant of INA203–INA205 Comparator 2 polarity                    | INA206-INA208 |

| Current-shunt monitor with single Comparator and V <sub>REF</sub> | INA200-INA202 |

| Current-shunt monitor only                                        | INA193-INA198 |

| Current-shunt monitor with split stages for filter options        | INA270-INA271 |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### ORDERING INFORMATION(1)

| PRODUCT | GAIN   | PACKAGE-<br>LEAD | PACKAGE<br>DESIGNATOR | PACKAGE<br>MARKING | 1.2V<br>REF OUT | EXTERNAL<br>COMP1 AND<br>COMP2<br>REF INPUTS | INTERNAL<br>COMP1 AND<br>COMP2<br>0.6V REF | COMP2<br>DELAY<br>PIN |

|---------|--------|------------------|-----------------------|--------------------|-----------------|----------------------------------------------|--------------------------------------------|-----------------------|

|         |        | SO-14            | D                     | INA203A            | Х               | Х                                            | X                                          | Х                     |

| INA203  | 20V/V  | MSOP-10          | DGS                   | BQN                |                 |                                              | X                                          |                       |

|         |        | TSSOP-14         | PW                    | INA203A            | Х               | Х                                            | X                                          | Х                     |

|         |        | SO-14            | D                     | INA204A            | Х               | Х                                            | Х                                          | Х                     |

| INA204  | 50V/V  | MSOP-10          | DGS                   | BQO                |                 |                                              | Х                                          |                       |

|         |        | TSSOP-14         | PW                    | INA204A            | Х               | Х                                            | X                                          | Х                     |

|         |        | SO-14            | D                     | INA205A            | Х               | Х                                            | X                                          | Х                     |

| INA205  | 100V/V | MSOP-10          | DGS                   | BQP                |                 |                                              | Х                                          |                       |

|         |        | TSSOP-14         | PW                    | INA205A            | Х               | Х                                            | Х                                          | Х                     |

<sup>(1)</sup> For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

#### ABSOLUTE MAXIMUM RATINGS(1)

|                                               |                                                        | INA203, INA204, INA205  | UNIT |

|-----------------------------------------------|--------------------------------------------------------|-------------------------|------|

| Supply Voltage, V+                            |                                                        | 18                      | V    |

| Current-Shunt Monitor Analog                  | Differential (V <sub>IN+</sub> ) – (V <sub>IN</sub> –) | -18 to +18              | V    |

| Inputs, V <sub>IN+</sub> and V <sub>IN-</sub> | Common-Mode                                            | -16 to +80              | V    |

| Comparator Analog Input and Re                | set Pins                                               | GND – 0.3 to (V+) + 0.3 | V    |

| Analog Output, Out Pin                        |                                                        | GND – 0.3 to (V+) + 0.3 | V    |

| Comparator Output, Out Pin                    |                                                        | GND – 0.3 to 18         | V    |

| V <sub>REF</sub> and CMP2 Delay Pin           |                                                        | GND – 0.3 to 10         | V    |

| Input Current Into Any Pin                    |                                                        | 5                       | mA   |

| Operating Temperature                         |                                                        | -55 to +150             | °C   |

| Storage Temperature                           |                                                        | -65 to +150             | °C   |

| Junction Temperature                          |                                                        | +150                    | °C   |

| ECD Detinana                                  | Human Body Model (HBM)                                 | 4000                    | V    |

| ESD Ratings                                   | Charged Device Model (CDM)                             | 500                     | V    |

<sup>(1)</sup> Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not supported.

Submit Documentation Feedback

Copyright © 2007, Texas Instruments Incorporated

#### **ELECTRICAL CHARACTERISTICS: CURRENT-SHUNT MONITOR**

**Boldface** limits apply over the specified temperature range:  $T_A = -40$ °C to +125°C.

At  $T_A$  = +25°C,  $V_S$  = +12V,  $V_{CM}$  = +12V,  $V_{SENSE}$  = 100mV,  $R_L$  = 10k $\Omega$  to GND,  $R_{PULL-UP}$  = 5.1k $\Omega$  each connected from CMP1 OUT and CMP2 OUT to  $V_S$ , and CMP1 IN+ = 1V and CMP2 IN- = GND, unless otherwise noted.

|                                                                       |                      |                                                                                    |     | INA203, INA204, IN          | A205                         |         |  |

|-----------------------------------------------------------------------|----------------------|------------------------------------------------------------------------------------|-----|-----------------------------|------------------------------|---------|--|

| CURRENT-SHUNT MONITOR PARA                                            | AMETERS              | CONDITIONS                                                                         | MIN | TYP                         | MAX                          | UNIT    |  |

| INPUT                                                                 |                      |                                                                                    |     |                             |                              |         |  |

| Full-Scale Sense Input Voltage                                        | V <sub>SENSE</sub>   | $V_{SENSE} = V_{IN+} - V_{IN-}$                                                    |     | 0.15                        | (V <sub>S</sub> - 0.25)/Gain | V       |  |

| Common-Mode Input Range                                               | V <sub>CM</sub>      |                                                                                    | -16 |                             | 80                           | V       |  |

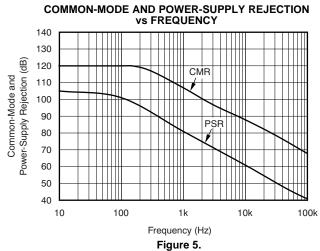

| Common-Mode Rejection Ratio                                           | CMRR                 | $V_{CM} = -16V \text{ to } +80V$                                                   | 80  | 100                         |                              | dB      |  |

| Over Temperature                                                      |                      | $V_{CM} = +12V \text{ to } +80V$                                                   | 100 | 123                         |                              | dB      |  |

| Offset Voltage, RTI <sup>(1)</sup>                                    | Vos                  |                                                                                    |     | ±0.5                        | ±2.5                         | mV      |  |

| +25°C to +125°C                                                       |                      |                                                                                    |     |                             | ±3                           | mV      |  |

| –40°C to +25°C                                                        |                      |                                                                                    |     |                             | ±3.5                         | mV      |  |

| vs Temperature                                                        | dV <sub>OS</sub> /dT | T <sub>MIN</sub> to T <sub>MAX</sub>                                               |     | 5                           |                              | μV/°C   |  |

| vs Power Supply                                                       | PSR                  | $V_{OUT} = 2V, V_{CM} = +18V, 2.7V$                                                |     | 2.5                         | 100                          | μ۷/۷    |  |

| Input Bias Current, V <sub>IN</sub> _ Pin                             | I <sub>B</sub>       |                                                                                    |     | ±9                          | ±16                          | μΑ      |  |

| OUTPUT (V <sub>SENSE</sub> ≥ 20mV)                                    |                      |                                                                                    |     |                             |                              |         |  |

| Gain:                                                                 | G                    |                                                                                    |     |                             |                              |         |  |

| INA203                                                                |                      |                                                                                    |     | 20                          |                              | V/V     |  |

| INA204                                                                |                      |                                                                                    |     | 50                          |                              | V/V     |  |

| INA205                                                                |                      |                                                                                    |     | 100                         |                              | V/V     |  |

| Gain Error                                                            |                      | V <sub>SENSE</sub> = 20mV to 100mV                                                 |     | ±0.2                        | ±1                           | %       |  |

| Over Temperature                                                      |                      | V <sub>SENSE</sub> = 20mV to 100mV                                                 |     |                             | ±2                           | %       |  |

| Total Output Error (2)                                                |                      | $V_{SENSE} = 120 \text{mV}, V_S = +16 \text{V}$                                    |     | ±0.75                       | ±2.2                         | %       |  |

| Over Temperature                                                      |                      | V <sub>SENSE</sub> = 120mV, V <sub>S</sub> = +16V                                  |     |                             | ±3.5                         | %       |  |

| Nonlinearity Error <sup>(3)</sup>                                     |                      | V <sub>SENSE</sub> = 20mV to 100mV                                                 |     | ±0.002                      |                              | %       |  |

| Output Impedance, Pin 2                                               | Ro                   | SENSE ZSIII (S 100III)                                                             |     | 1.5                         |                              | Ω       |  |

| Maximum Capacitive Load                                               | 0                    | No Sustained Oscillation                                                           |     | 10                          |                              | nF      |  |

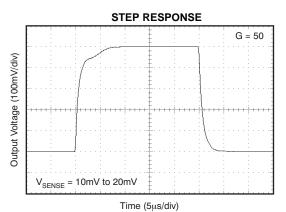

| OUTPUT (V <sub>SENSE</sub> < 20mV) <sup>(4)</sup>                     |                      | 110 Gustamou Gustiation                                                            |     | 10                          |                              |         |  |

| INA203, INA204, INA205                                                |                      | $-16V \le V_{CM} < 0V$                                                             |     | 300                         |                              | mV      |  |

| INA203                                                                |                      | $0V \le V_{CM} \le V_S, V_S = 5V$                                                  |     | 300                         | 0.4                          | V       |  |

| INA204                                                                |                      | $0V \le V_{CM} \le V_{S}, V_{S} = 5V$<br>$0V \le V_{CM} \le V_{S}, V_{S} = 5V$     |     |                             | 1                            | V       |  |

| INA205                                                                |                      | $0V \le V_{CM} \le V_S, V_S = 5V$ $0V \le V_{CM} \le V_S, V_S = 5V$                |     |                             | 2                            | V       |  |

| INA203<br>INA203, INA204, INA205                                      |                      | $V_{\rm S} < V_{\rm CM} \le 80V$                                                   |     | 300                         | 2                            | mV      |  |

| VOLTAGE OUTPUT <sup>(5)</sup>                                         |                      | VS C VCM = 60 V                                                                    |     | 300                         |                              | IIIV    |  |

| Output Swing to the Positive Rail                                     |                      | V <sub>IN-</sub> = 11V, V <sub>IN+</sub> = 12V                                     |     | ()(.) 0.15                  | (//.) 0.25                   | v       |  |

| Output Swing to the Positive Rail  Output Swing to GND <sup>(6)</sup> |                      |                                                                                    |     | (V+) - 0.15                 | (V+) - 0.25                  | v       |  |

| FREQUENCY RESPONSE                                                    |                      | $V_{IN-} = 0V, V_{IN+} = -0.5V$                                                    |     | (V <sub>GND</sub> ) + 0.004 | $(V_{GND}) + 0.05$           | v       |  |

|                                                                       | DW                   |                                                                                    |     |                             |                              |         |  |

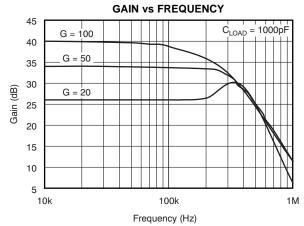

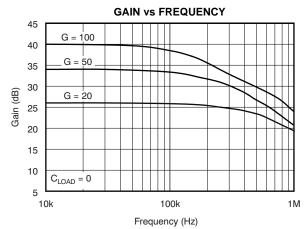

| Bandwidth:                                                            | BW                   | C 525                                                                              |     | FOO                         |                              | LI I≕   |  |

| INA203                                                                |                      | $C_{LOAD} = 5pF$                                                                   |     | 500                         |                              | kHz     |  |

| INA204                                                                |                      | $C_{LOAD} = 5pF$                                                                   |     | 300                         |                              | kHz     |  |

| INA205                                                                |                      | $C_{LOAD} = 5pF$                                                                   |     | 200                         |                              | kHz     |  |

| Phase Margin                                                          | 0.5                  | $C_{LOAD}$ < 10nF                                                                  |     | 40                          |                              | Degrees |  |

| Slew Rate                                                             | SR                   |                                                                                    |     | 1                           |                              | V/µs    |  |

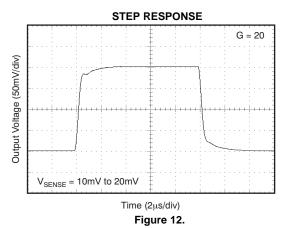

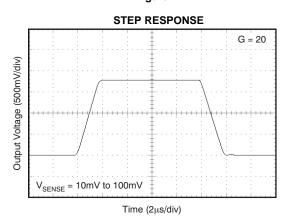

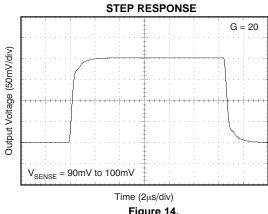

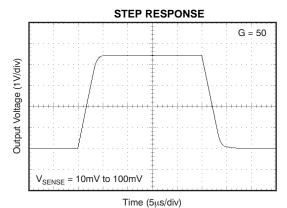

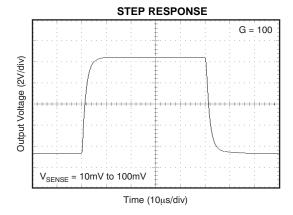

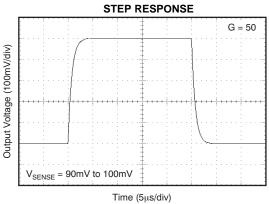

| Settling Time (1%)                                                    |                      | $V_{SENSE} = 10 \text{mV}_{PP}$ to $100 \text{mV}_{PP}$ , $C_{LOAD} = 5 \text{pF}$ |     | 2                           |                              | μs      |  |

| NOISE, RTI                                                            |                      |                                                                                    |     |                             |                              | . =     |  |

| Output Voltage Noise Density                                          |                      |                                                                                    |     | 40                          |                              | nV/√Hz  |  |

Offset is extrapolated from measurements of the output at 20mV and 100mV  $V_{SENSE}$ .

<sup>(2)</sup> Total output error includes effects of gain error and V<sub>OS</sub>.

Linearity is best fit to a straight line.

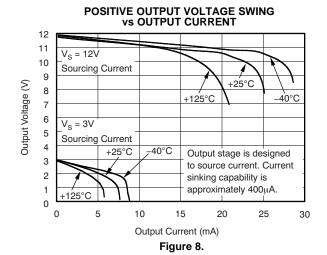

For details on this region of operation, see the Accuracy Variations section in the Applications Information. See Typical Characteristic curve Positive Output Voltage Swing vs Output Current (Figure 8).

<sup>(5)</sup>

Specified by design; not production tested.

#### **ELECTRICAL CHARACTERISTICS: COMPARATOR**

**Boldface** limits apply over the specified temperature range:  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ .

At  $T_A$  = +25°C,  $V_S$  = +12V,  $V_{CM}$  = +12V,  $V_{SENSE}$  = 100mV,  $R_L$  = 10k $\Omega$  to GND, and  $R_{PULL-UP}$  = 5.1k $\Omega$  each connected from CMP1 OUT and CMP2 OUT to  $V_S$ , unless otherwise noted.

|                                         |                |                                                                                      | IN  | IA203, INA204, INA2         | 05  |       |

|-----------------------------------------|----------------|--------------------------------------------------------------------------------------|-----|-----------------------------|-----|-------|

| COMPARATOR PARAMETERS                   |                | CONDITIONS                                                                           | MIN | TYP                         | MAX | UNIT  |

| OFFSET VOLTAGE                          |                |                                                                                      |     |                             |     |       |

| Offset Voltage                          |                | Comparator Common-Mode Voltage = Threshold Voltage                                   |     | 2                           |     | mV    |

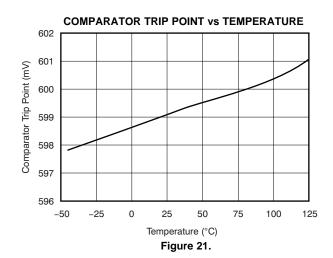

| Offset Voltage Drift, Comparator        | 1              |                                                                                      |     | ±2                          |     | μV/°C |

| Offset Voltage Drift, Comparator        | 2              |                                                                                      |     | +5.4                        |     | μV/°C |

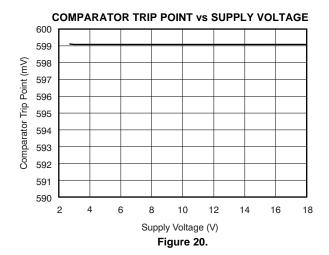

| Threshold                               |                | $T_A = +25^{\circ}C$                                                                 | 590 | 608                         | 620 | mV    |

| Over Temperature                        |                |                                                                                      | 586 |                             | 625 | mV    |

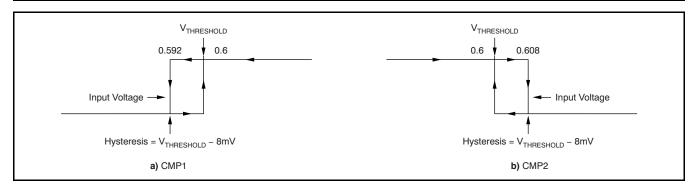

| Hysteresis <sup>(1)</sup> , CMP1        |                | $T_A = -40^{\circ}C$ to $+85^{\circ}C$                                               |     | -8                          |     | mV    |

| Hysteresis <sup>(1)</sup> , CMP2        |                | $T_A = -40^{\circ}C$ to $+85^{\circ}C$                                               |     | 8                           |     | mV    |

| INPUT BIAS CURRENT(2)                   |                |                                                                                      |     |                             |     |       |

| CMP1 IN+, CMP2 IN+                      |                |                                                                                      |     | 0.005                       | 10  | nA    |

| vs Temperature                          |                |                                                                                      |     |                             | 15  | nA    |

| INPUT IMPEDANCE                         |                |                                                                                      |     |                             |     |       |

| Pins 3 and 6 (14-pin packages only)     |                |                                                                                      |     | 10                          |     | kΩ    |

| INPUT RANGE                             |                |                                                                                      |     |                             |     |       |

| CMP1 IN+ and CMP2 IN+                   |                |                                                                                      |     | 0V to V <sub>S</sub> – 1.5V |     | V     |

| Pins 3 and 6 (14-pin packages only) (3) | ,              |                                                                                      |     | 0V to V <sub>S</sub> – 1.5V |     | V     |

| OUTPUT                                  |                |                                                                                      |     |                             |     |       |

| Large-Signal Differential Voltage Gain  |                | CMP $V_{OUT}$ 1V to 4V, $R_L \ge 15k\Omega$ Connected to 5V                          |     | 200                         |     | V/mV  |

| High-Level Output Current               |                | $V_{ID} = 0.4V$ , $V_{OH} = V_{S}$                                                   |     | 0.0001                      | 1   | μΑ    |

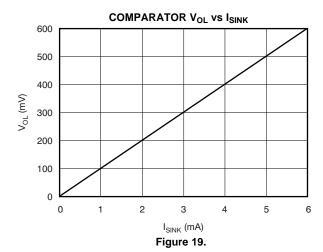

| Low-Level Output Voltage                |                | $V_{ID} = -0.6V$ , $I_{OL} = 2.35mA$                                                 |     | 220                         | 300 | mV    |

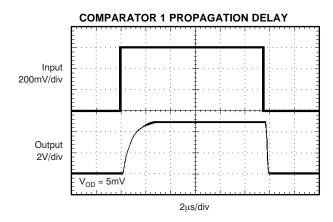

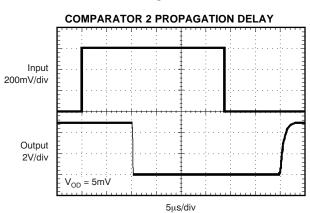

| RESPONSE TIME <sup>(4)</sup>            |                |                                                                                      |     |                             |     |       |

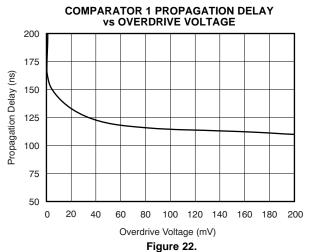

| Comparator 1                            |                | $R_L$ to 5V, $C_L$ = 15pF, 100mV Input Step with 5mV Overdrive                       |     | 1.3                         |     | μs    |

| Comparator 2                            |                | $R_L$ to 5V, $C_L$ = 15pF, 100mV Input Step with 5mV Overdrive, $C_{DELAY}$ Pin Open |     | 1.3                         |     | μs    |

| RESET                                   |                |                                                                                      |     |                             |     |       |

| RESET Threshold <sup>(5)</sup>          |                |                                                                                      |     | 1.1                         |     | V     |

| Logic Input Impedance                   |                |                                                                                      |     | 2                           |     | ΜΩ    |

| Minimum RESET Pulse Width               |                |                                                                                      |     | 1.5                         |     | μs    |

| RESET Propagation Delay                 |                |                                                                                      |     | 3                           |     | μs    |

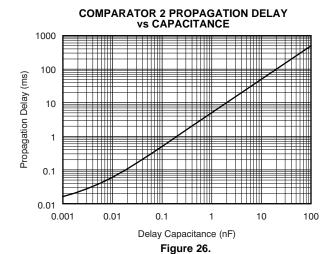

| Comparator 2 Delay Equation (6)         |                |                                                                                      |     | $C_{DELAY} = t_D/5$         |     | μF    |

| Comparator 2 Delay                      | t <sub>D</sub> | $C_{DELAY} = 0.1 \mu F$                                                              |     | 0.5                         |     | s     |

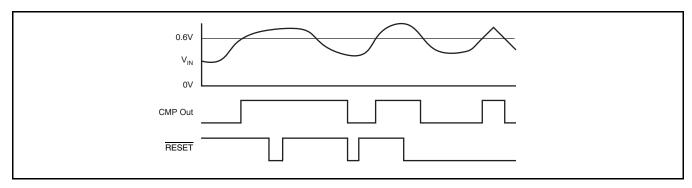

<sup>(1)</sup> Hysteresis refers to the threshold (the threshold specification applies to a rising edge of a noninverting input) of a falling edge on the noninverting input of the comparator; refer to Figure 1.

(2) Specified by design; not production tested.

(6) The Comparator 2 delay applies to both rising and falling edges of the comparator output.

<sup>(3)</sup> See the Comparator Maximum Input Voltage Range section in the Applications Information.

<sup>(4)</sup> The comparator response time specified is the interval between the input step function and the instant when the output crosses 1.4V.

<sup>(5)</sup> The CMP1 RESET input has an internal 2MΩ (typical) pull-down. Leaving the CMP1 RESET open results in a LOW state, with transparent comparator operation.

Figure 1. Comparator Hysteresis

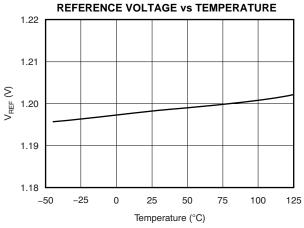

#### **ELECTRICAL CHARACTERISTICS: REFERENCE**

**Boldface** limits apply over the specified temperature range:  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ .

At  $T_A$  = +25°C,  $V_S$  = +12V,  $V_{CM}$  = +12V,  $V_{SENSE}$  = 100mV,  $R_L$  = 10k $\Omega$  to GND, and  $R_{PULL-UP}$  = 5.1k $\Omega$  each connected from CMP1 OUT and CMP2 OUT to  $V_S$ , unless otherwise noted.

|                                                                    |                       |                                        | INA203 | , INA204, | INA205 |        |

|--------------------------------------------------------------------|-----------------------|----------------------------------------|--------|-----------|--------|--------|

| REFERENCE PARAMETERS                                               |                       | CONDITIONS                             | MIN    | TYP       | MAX    | UNIT   |

| REFERENCE VOLTAGE                                                  |                       |                                        |        |           |        |        |

| 1.2V <sub>REFOUT</sub> Output Voltage                              |                       |                                        | 1.188  | 1.2       | 1.212  | V      |

| Reference Drift                                                    | dV <sub>OUT</sub> /dT | $T_A = -40^{\circ}C$ to $+85^{\circ}C$ |        | 40        | 100    | ppm/°C |

| 0.6V <sub>REF</sub> Output Voltage (Pins 3 and 6 of 14-pin package | jes only)             |                                        |        | 0.6       |        | V      |

| Reference Drift                                                    | dV <sub>OUT</sub> /dT | $T_A = -40^{\circ}C$ to $+85^{\circ}C$ |        | 40        | 100    | ppm/°C |

| LOAD REGULATION                                                    | $dV_{OUT}/dI_{LOAD}$  |                                        |        |           |        |        |

| Sourcing                                                           |                       | $0mA < I_{SOURCE} < 0.5mA$             |        | 0.4       | 2      | mV/mA  |

| Sinking                                                            |                       | $0mA < I_{SINK} < 0.5mA$               |        | 0.4       |        | mV/mA  |

| LOAD CURRENT                                                       | I <sub>LOAD</sub>     |                                        |        | 1         |        | mA     |

| LINE REGULATION                                                    | $dV_{OUT}/dV_{S}$     | $2.7V < V_S < 18V$                     |        | 30        |        | μV/V   |

| CAPACITIVE LOAD                                                    |                       |                                        |        |           |        |        |

| Reference Output Maximum Capacitive Load                           |                       | No Sustained Oscillations              |        | 10        |        | nF     |

| OUTPUT IMPEDANCE                                                   |                       |                                        |        |           |        |        |

| Pins 3 and 6 of 14-Pin Packages Only                               |                       |                                        |        | 10        |        | kΩ     |

#### **ELECTRICAL CHARACTERISTICS: GENERAL**

**Boldface** limits apply over the specified temperature range:  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ .

All specifications at  $T_A$  = +25°C,  $V_S$  = +12V,  $V_{CM}$  = +12V,  $V_{SENSE}$  = 100mV,  $R_L$  = 10k $\Omega$  to GND,  $R_{PULL-UP}$  = 5.1k $\Omega$  each connected from CMP1 OUT and CMP2 OUT to  $V_S$ , and CMP1 IN+ = 1V and CMP2 IN- = GND, unless otherwise noted.

|                                                    |                    |                                                   | INA2        | 03, INA204, IN | NA205 |      |  |

|----------------------------------------------------|--------------------|---------------------------------------------------|-------------|----------------|-------|------|--|

| GENERAL PARAMETERS                                 | GENERAL PARAMETERS |                                                   | MIN         | TYP            | MAX   | UNIT |  |

| POWER SUPPLY                                       |                    |                                                   |             |                |       |      |  |

| Operating Power Supply                             | ٧s                 |                                                   | +2.7        |                | +18   | V    |  |

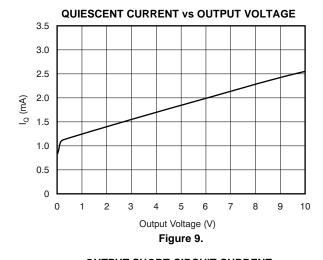

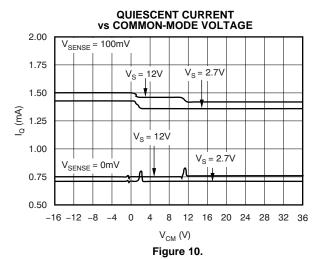

| Quiescent Current                                  | IQ                 | $V_{OUT} = 2V$                                    |             | 1.8            | 2.2   | mA   |  |

| Over Temperature                                   |                    | V <sub>OUT</sub> = 2V<br>V <sub>SENSE</sub> = 0mV |             |                | 2.8   | mA   |  |

| Comparator Power-On Reset Threshold <sup>(1)</sup> |                    |                                                   |             | 1.5            |       | V    |  |

| TEMPERATURE                                        |                    |                                                   |             |                |       |      |  |

| Specified Temperature Range                        |                    |                                                   | -40         |                | +125  | °C   |  |

| Operating Temperature Range                        |                    |                                                   | <b>–</b> 55 |                | +150  | °C   |  |

| Storage Temperature Range                          |                    |                                                   | -65         |                | +150  | °C   |  |

| Thermal Resistance                                 | $\theta_{JA}$      |                                                   |             |                |       |      |  |

| MSOP-10 Surface-Mount                              |                    |                                                   |             | 200            |       | °C/W |  |

| SO-14, TSSOP-14 Surface-Mount                      |                    |                                                   |             | 150            |       | °C/W |  |

<sup>(1)</sup> The INA203, INA204, and INA205 are designed to power-up with the comparator in a defined reset state as long as CMP1 RESET is open or grounded. The comparator will be in reset as long as the power supply is below the voltage shown here. The comparator assumes a state based on the comparator input above this supply voltage. If CMP1 RESET is high at power-up, the comparator output comes up high and requires a reset to assume a low state, if appropriate.

Submit Documentation Feedback

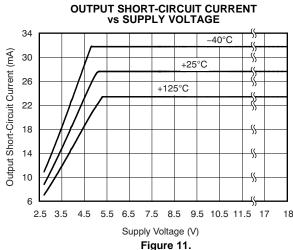

#### TYPICAL CHARACTERISTICS

All specifications at  $T_A = +25$ °C,  $V_S = +12$ V,  $V_{CM} = +12$ V, and  $V_{SENSE} = 100$ mV, unless otherwise noted.

Figure 2.

Figure 3.

error of the ideal output value) 3.5

4.0

3.0

2.5

2.0

1.5

1.0

0.5

0

50

100 150

Total Output Error

TOTAL OUTPUT ERROR vs  $V_{\text{SENSE}}$

V<sub>SENSE</sub> (mV) Figure 6.

250 300

350

400 450 500

200

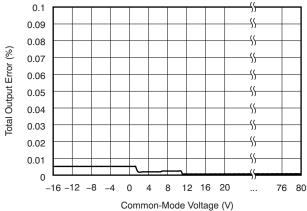

**TOTAL OUTPUT ERROR vs COMMON-MODE VOLTAGE**

Figure 7.

All specifications at  $T_A = +25$ °C,  $V_S = +12$ V,  $V_{CM} = +12$ V, and  $V_{SENSE} = 100$ mV, unless otherwise noted.

Figure 13.

All specifications at  $T_A = +25$ °C,  $V_S = +12$ V,  $V_{CM} = +12$ V, and  $V_{SENSE} = 100$ mV, unless otherwise noted.

Figure 14.

Figure 16.

Figure 18.

Figure 15.

Figure 17.

Copyright © 2007, Texas Instruments Incorporated

All specifications at  $T_A = +25$ °C,  $V_S = +12$ V,  $V_{CM} = +12$ V, and  $V_{SENSE} = 100$ mV, unless otherwise noted.

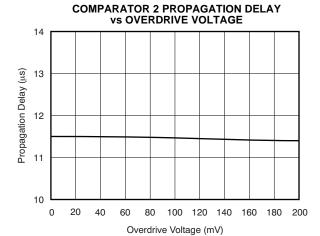

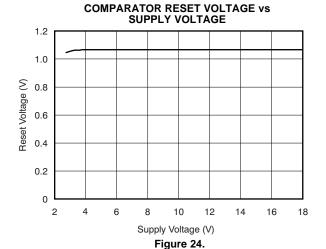

Figure 23.

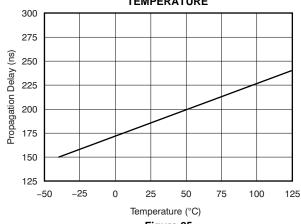

Figure 25.

All specifications at  $T_A$  = +25°C,  $V_S$  = +12V,  $V_{CM}$  = +12V, and  $V_{SENSE}$  = 100mV, unless otherwise noted.

Figure 27.

Figure 28.

#### **APPLICATIONS INFORMATION**

#### **BASIC CONNECTIONS**

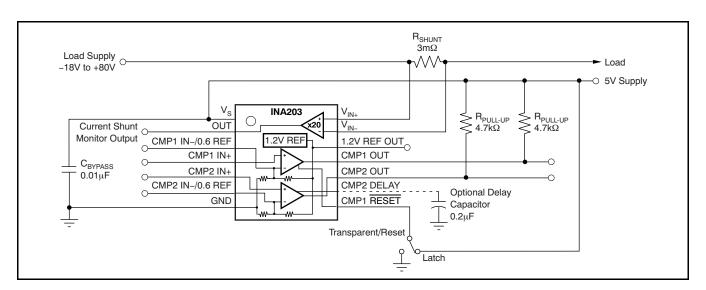

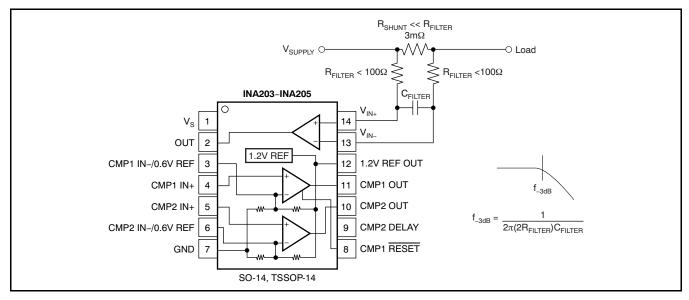

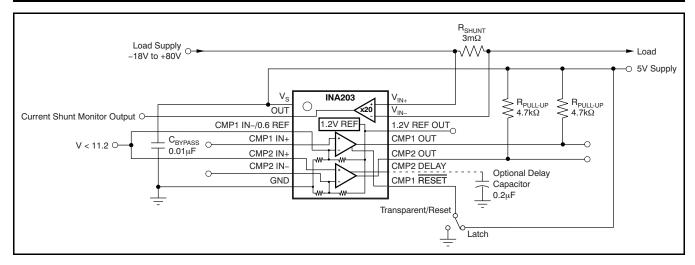

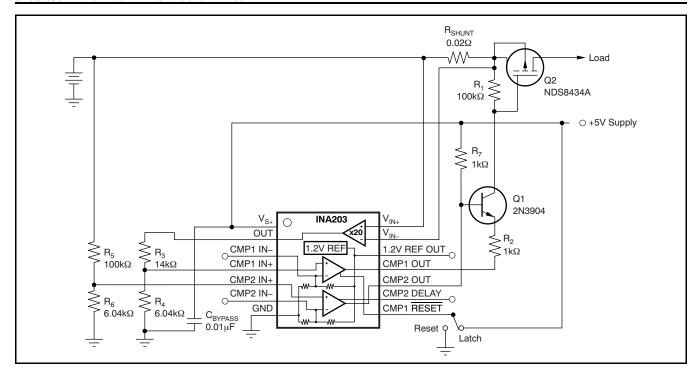

Figure 30 shows the basic connections of the INA203, INA204, and INA205. The input pins,  $V_{IN+}$  and  $V_{IN-}$ , should be connected as closely as possible to the shunt resistor to minimize any resistance in series with the shunt resistance.

Power-supply bypass capacitors are required for stability. Applications with noisy or high-impedance power supplies may require additional decoupling capacitors to reject power-supply noise. Connect bypass capacitors close to the device pins.

#### **POWER SUPPLY**

The input circuitry of the INA203, INA204, and INA205 can accurately measure beyond the power-supply voltage, V+. For example, the V+ power supply can be 5V, whereas the load power-supply voltage is up to +80V. The output voltage range of the OUT terminal, however, is limited by the voltages on the power-supply pin.

# ACCURACY VARIATIONS AS A RESULT OF VSENSE AND COMMON-MODE VOLTAGE

The accuracy of the INA203, INA204, and INA205 current shunt monitors is a function of two main variables:  $V_{SENSE}$  ( $V_{IN+}$  –  $V_{IN-}$ ) and common-mode voltage,  $V_{CM}$ , relative to the supply voltage,  $V_{S}$ .  $V_{CM}$  is expressed as ( $V_{IN+}$  +  $V_{IN-}$ )/2; however, in practice,  $V_{CM}$  is seen as the voltage at  $V_{IN+}$  because the voltage drop across  $V_{SENSE}$  is usually small.

This section addresses the accuracy of these specific operating regions:

- Normal Case 1: V<sub>SENSE</sub> ≥ 20mV, V<sub>CM</sub> ≥ V<sub>S</sub>

- Normal Case 2: V<sub>SENSE</sub> ≥ 20mV, V<sub>CM</sub> < V<sub>S</sub>

- Low V<sub>SENSE</sub> Case 1: V<sub>SENSE</sub> < 20mV, −16V ≤ V<sub>CM</sub>

< 0</li>

- Low  $V_{SENSE}$  Case 2:  $V_{SENSE}$  < 20mV, 0V  $\leq$   $V_{CM} \leq$   $V_{S}$

- Low V<sub>SENSE</sub> Case 3: V<sub>SENSE</sub> < 20mV, V<sub>S</sub> < V<sub>CM</sub> ≤ 80V

#### Normal Case 1: V<sub>SENSE</sub> ≥ 20mV, V<sub>CM</sub> ≥ V<sub>S</sub>

This region of operation provides the highest accuracy. Here, the input offset voltage is characterized and measured using a two-step method. First, the gain is determined by Equation 1.

$$G = \frac{V_{OUT1} - V_{OUT2}}{100mV - 20mV}$$

(1)

where:

$V_{OUT1} = Output Voltage with V_{SENSE} = 100mV$

$V_{OUT2}$  = Output Voltage with  $V_{SENSE}$  = 20mV

Then the offset voltage is measured at  $V_{SENSE} = 100 \text{mV}$  and referred to the input (RTI) of the current shunt monitor, as shown in Equation 2.

$$V_{OS}RTI$$

(Referred-To-Input) =  $\left[\frac{V_{OUT1}}{G}\right] - 100mV$  (2)

Figure 30. INA20x Basic Connection

In the Typical Characteristics, the *Output Error vs Common-Mode Voltage* curve (Figure 7) shows the highest accuracy for this region of operation. In this plot,  $V_S = 12V$ ; for  $V_{CM} \ge 12V$ , the output error is at its minimum. This case is also used to create the  $V_{SENSE} \ge 20\text{mV}$  output specifications in the Electrical Characteristics table.

#### Normal Case 2: V<sub>SENSE</sub> ≥ 20mV, V<sub>CM</sub> < V<sub>S</sub>

This region of operation has slightly less accuracy than Normal Case 1 as a result of the common-mode operating area in which the part functions, as seen in the *Output Error vs Common-Mode Voltage* curve (Figure 7). As noted, for this graph  $V_S = 12V$ ; for  $V_{CM} < 12V$ , the Output Error increases as  $V_{CM}$  becomes less than 12V, with a typical maximum error of 0.005% at the most negative  $V_{CM} = -16V$ .

#### Low V<sub>SENSE</sub> Case 1:

$V_{SENSE} < 20mV, -16V \leq V_{CM} < 0;$  and Low  $V_{SENSE}$  Case 3:  $V_{SENSE} < 20mV, \, V_S < V_{CM} \leq 80V$

Although the INA203 family of devices are not designed for accurate operation in either of these regions, some applications are exposed to these conditions; for example, when monitoring power supplies that are switched on and off while  $V_{\rm S}$  is still applied to the INA203, INA204, or INA205. It is important to know what the behavior of the devices will be in these regions.

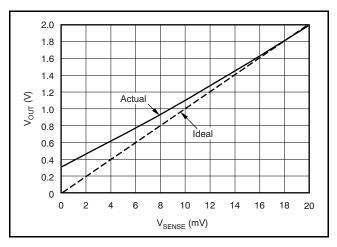

As  $V_{SENSE}$  approaches 0mV, in these  $V_{CM}$  regions, the device output accuracy degrades. A larger-than-normal offset can appear at the current shunt monitor output with a typical maximum value of  $V_{OUT} = 300$ mV for  $V_{SENSE} = 0$ mV. As  $V_{SENSE}$  approaches 20mV,  $V_{OUT}$  returns to the expected output value with accuracy as specified in the Electrical Characteristics. Figure 31 illustrates this effect using the INA205 (Gain = 100).

Figure 31. Example for Low V<sub>SENSE</sub> Cases 1 and 3 (INA205, Gain = 100)

#### Low V<sub>SENSE</sub> Case 2: V<sub>SENSE</sub> < 20mV, 0V ≤ V<sub>CM</sub> ≤ V<sub>S</sub>

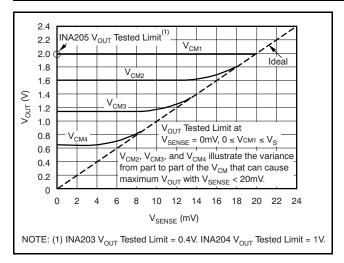

This region of operation is the least accurate for the INA203 family. To achieve the wide input common-mode voltage range, these devices use two op amp front ends in parallel. One op amp front end operates in the positive input common-mode voltage range, and the other in the negative input region. For this case, neither of these two internal amplifiers dominates and overall loop gain is very low. Within this region, V<sub>OUT</sub> approaches voltages close to linear operation levels for Normal Case 2. This deviation from linear operation becomes greatest the closer V<sub>SENSE</sub> approaches 0V. Within this region, as V<sub>SENSE</sub> approaches 20mV, device operation is closer to that described by Normal Case 2. Figure 32 illustrates this behavior for the INA205. The V<sub>OUT</sub> maximum peak for this case is tested by maintaining a constant V<sub>S</sub>, setting  $V_{SENSE} = 0mV$ , and sweeping  $V_{CM}$  from 0V to V<sub>S</sub>. The exact V<sub>CM</sub> at which V<sub>OUT</sub> peaks during this test varies from part to part, but the V<sub>OUT</sub> maximum peak is tested to be less than the specified  $V_{OLIT}$ Tested Limit.

Figure 32. Example for Low V<sub>SENSE</sub> Case 2 (INA205, Gain = 100)

#### **SELECTING R<sub>SHUNT</sub>**

The value chosen for the shunt resistor,  $R_{SHUNT}$ , depends on the application and is a compromise between small-signal accuracy and maximum permissible voltage loss in the measurement line. High values of  $R_{SHUNT}$  provide better accuracy at lower currents by minimizing the effects of offset, while low values of  $R_{SHUNT}$  minimize voltage loss in the supply line. For most applications, best performance is attained with an  $R_{SHUNT}$  value that provides a full-scale shunt voltage range of 50mV to 100mV. Maximum input voltage for accurate measurements is  $(V_{SHUNT}-0.25)/Gain$ .

#### TRANSIENT PROTECTION

The -16V to +80V common-mode range of the INA203, INA204, and INA205 is ideal for withstanding automotive fault conditions ranging from 12V battery reversal up to +80V transients, since no additional protective components are needed up to those levels. In the event that the INA203, INA204, and INA205 are exposed to transients on the inputs in excess of their ratings, then external transient absorption with semiconductor transient absorbers (zeners or *Transzorbs*) are necessary. Use of metal oxide varistors (MOVs) or video disk recorders (VDRs) is not recommended except when they are used in addition to a semiconductor transient absorber. Select the transient absorber such that it will never allow the INA203, INA204, and INA205 to be exposed to transients greater than +80V (that is,

allow for transient absorber tolerance, as well as additional voltage because of transient absorber dynamic impedance). Despite the use of internal zener-type ESD protection, the INA203, INA204, and INA205 do not lend themselves to using external resistors in series with the inputs because the internal gain resistors can vary up to ±30% but are closely matched. (If gain accuracy is not important, then resistors can be added in series with the INA203, INA204, and INA205 inputs with two equal resistors on each input.)

#### **OUTPUT VOLTAGE RANGE**

The output of the INA203, INA204, and INA205 is accurate within the output voltage swing range set by the power-supply pin, V+. This performance is best illustrated when using the INA205 (a gain of 100 version), where a 100mV full-scale input from the shunt resistor requires an output voltage swing of +10V, and a power-supply voltage sufficient to achieve +10V on the output.

#### INPUT FILTERING

An obvious and straightforward location for filtering is at the output of the INA203, INA204, and INA205 series; however, this location negates the advantage of the low output impedance of the internal buffer. The only other option for filtering is at the input pins of the INA203, INA204, and INA205, which is complicated by the internal  $5k\Omega+30\%$  input impedance; this configuration is illustrated in Figure 33. Using the lowest possible resistor values minimizes both the initial shift in gain and effects of tolerance. The effect on initial gain is given by Equation 3:

Gain Error % = 100 -

$$\left[100 \times \frac{5k\Omega}{5k\Omega + R_{FILT}}\right]$$

(3)

Total effect on gain error can be calculated by replacing the  $5k\Omega$  term with  $5k\Omega-30\%$ , (or  $3.5k\Omega)$  or  $5k\Omega+30\%$  (or  $6.5k\Omega)$ . The tolerance extremes of  $R_{\text{FILT}}$  can also be inserted into the equation. If a pair of  $100\Omega$  1% resistors are used on the inputs, the initial gain error will be 1.96%. Worst-case tolerance conditions will always occur at the lower excursion of the internal  $5k\Omega$  resistor  $(3.5k\Omega)$ , and the higher excursion of  $R_{\text{FILT}}-3\%$  in this case.

Figure 33. Input Filter (Gain Error: 1.5% to -2.2%)

Note that the specified accuracy of the INA203, INA204, and INA205 must then be combined in addition to these tolerances. While this discussion treated accuracy worst-case conditions by combining the extremes of the resistor values, it is appropriate to use geometric mean or root sum square calculations to total the effects of accuracy variations.

#### REFERENCE

The INA203, INA204, and INA205 include an internal voltage reference that has a load regulation of 0.4mV/mA (typical), and not more than 100ppm/°C of drift. Only the 14-pin package allows external access to reference voltages, where voltages of 1.2V and 0.6V are both available. Output current versus output voltage is illustrated in the Typical Characteristics section.

#### **COMPARATOR**

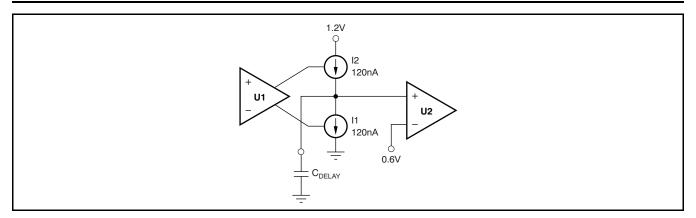

The INA203, INA204, and INA205 devices incorporate two open-drain comparators. These comparators typically have 2mV of offset and a 1.3µs (typical) response time. The output of Comparator 1 latches and is reset through the CMP1 RESET pin, as shown in Figure 35. This configuration applies to both the 10- and 14-pin versions. Figure 34 illustrates the comparator delay.

The 14-pin versions of the INA203, INA204, and

INA205 include additional features for comparator functions. The comparator reference voltage of both Comparator 1 and Comparator 2 can be overridden by external inputs for increased design flexibility. Comparator 2 has a programmable delay.

#### **COMPARATOR DELAY (14-Pin Version Only)**

The Comparator 2 programmable delay is controlled by a capacitor connected to the CMP2 Delay Pin; see Figure 30. The capacitor value (in  $\mu$ F) is selected by using Equation 4:

$$C_{DELAY} (in \mu F) = \frac{t_D}{5}$$

(4)

A simplified version of the delay circuit for Comparator 2 is shown in Figure 34. The delay comparator consists of two comparator stages with the delay between them. Note that I1 and I2 cannot be turned on simultaneously; I1 corresponds to a U1 low output and I2 corresponds to a U1 high output. Using an initial assumption that the U1 output is low, I1 is on, then U2 +IN is zero. If U1 goes high, I2 supplies 120nA to CDELAY. The voltage at U2 +IN begins to ramp toward a 0.6V threshold. When the voltage crosses this threshold, the U2 output goes high while the voltage at U2 +IN continues to ramp up to a maximum of 1.2V when given sufficient time (twice the value of the delay specified for CDELAY). This entire sequence is reversed when the comparator outputs go low, so that returning to low exhibits the same delay.

Figure 34. Simplified Model of the Comparator 2 Delay Circuit

Figure 35. Comparator Latching Capability

It is important to note what will happen if events occur more rapidly than the delay timeout; for example, when the U1 output goes high (turning on I2), but returns low (turning I1 back on) prior to reaching the 0.6V transition for U2. The voltage at U2 +IN ramps back down at a rate determined by the value of  $C_{\text{DELAY}}$ , and only returns to zero if given sufficient time.

In essence, when analyzing Comparator 2 for behavior with events more rapid than its delay setting, use the model shown in Figure 34.

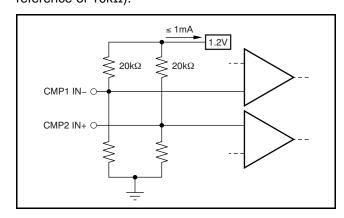

# COMPARATOR MAXIMUM INPUT VOLTAGE RANGE

The maximum voltage at the comparator input for normal operation is up to (V+) - 1.5V. There are special considerations when overdriving the reference inputs (pins 3 and 6). Driving either or both inputs high enough to drive 1mA back into the reference introduces errors into the reference. Figure 36 shows the basic input structure. A general guideline is to limit the voltage on both inputs to a total of 20V. The exact limit depends on the available voltage and

whether either or both inputs are subject to the large voltage. When making this determination, consider the  $20k\Omega$  from each input back to the comparator. Figure 37 shows the maximum input voltage that avoids creating a reference error when driving both inputs (an equivalent resistance back into the reference of  $10k\Omega$ ).

Figure 36. Limit Current Into Reference ≤ 1mA

Figure 37. Overdriving Comparator Inputs Without Generating a Reference Error

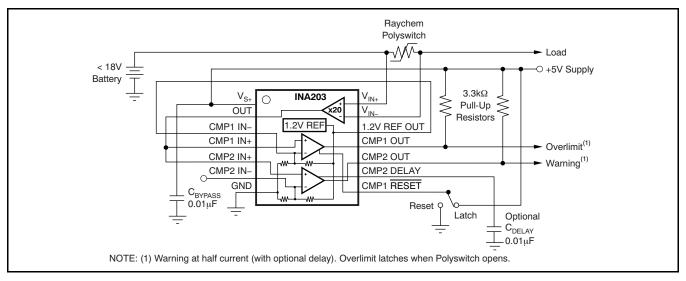

Figure 38. Polyswitch Warning and Fault Detection Circuit

Figure 39. Lead-Acid Battery Protection Circuit

#### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp (3)   |

|------------------|-----------------------|-----------------|--------------------|------|----------------|---------------------------|------------------|---------------------|

| INA203AID        | ACTIVE                | SOIC            | D                  | 14   | 50             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR |

| INA203AIDG4      | ACTIVE                | SOIC            | D                  | 14   | 50             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR |

| INA203AIDGSR     | ACTIVE                | MSOP            | DGS                | 10   | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR |

| INA203AIDGSRG4   | ACTIVE                | MSOP            | DGS                | 10   | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR |

| INA203AIDGST     | ACTIVE                | MSOP            | DGS                | 10   | 250            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR |

| INA203AIDGSTG4   | ACTIVE                | MSOP            | DGS                | 10   | 250            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR |

| INA203AIDR       | ACTIVE                | SOIC            | D                  | 14   | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR |

| INA203AIDRG4     | ACTIVE                | SOIC            | D                  | 14   | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR |

| INA203AIPW       | ACTIVE                | TSSOP           | PW                 | 14   | 90             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR |

| INA203AIPWG4     | ACTIVE                | TSSOP           | PW                 | 14   | 90             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR |

| INA203AIPWR      | ACTIVE                | TSSOP           | PW                 | 14   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR |

| INA203AIPWRG4    | ACTIVE                | TSSOP           | PW                 | 14   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR |

| INA204AID        | ACTIVE                | SOIC            | D                  | 14   | 50             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR |

| INA204AIDG4      | ACTIVE                | SOIC            | D                  | 14   | 50             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR |

| INA204AIDGSR     | ACTIVE                | MSOP            | DGS                | 10   | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR |

| INA204AIDGSRG4   | ACTIVE                | MSOP            | DGS                | 10   | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR |

| INA204AIDGST     | ACTIVE                | MSOP            | DGS                | 10   | 250            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR |

| INA204AIDGSTG4   | ACTIVE                | MSOP            | DGS                | 10   | 250            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR |

| INA204AIDR       | ACTIVE                | SOIC            | D                  | 14   | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR |

| INA204AIDRG4     | ACTIVE                | SOIC            | D                  | 14   | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR |

| INA204AIPW       | ACTIVE                | TSSOP           | PW                 | 14   | 90             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR |

| INA204AIPWG4     | ACTIVE                | TSSOP           | PW                 | 14   | 90             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR |

| INA204AIPWR      | ACTIVE                | TSSOP           | PW                 | 14   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR |

| INA204AIPWRG4    | ACTIVE                | TSSOP           | PW                 | 14   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR |

| INA205AID        | ACTIVE                | SOIC            | D                  | 14   | 50             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR |

.com 19-Nov-2007

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|---------------------------|------------------|------------------------------|

| INA205AIDG4      | ACTIVE                | SOIC            | D                  | 14   | 50             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| INA205AIDGSR     | ACTIVE                | MSOP            | DGS                | 10   | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| INA205AIDGSRG4   | ACTIVE                | MSOP            | DGS                | 10   | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| INA205AIDGST     | ACTIVE                | MSOP            | DGS                | 10   | 250            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| INA205AIDGSTG4   | ACTIVE                | MSOP            | DGS                | 10   | 250            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| INA205AIDR       | ACTIVE                | SOIC            | D                  | 14   | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| INA205AIDRG4     | ACTIVE                | SOIC            | D                  | 14   | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| INA205AIPW       | ACTIVE                | TSSOP           | PW                 | 14   | 90             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| INA205AIPWG4     | ACTIVE                | TSSOP           | PW                 | 14   | 90             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| INA205AIPWR      | ACTIVE                | TSSOP           | PW                 | 14   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| INA205AIPWRG4    | ACTIVE                | TSSOP           | PW                 | 14   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

w.ti.com 4-Apr-2008

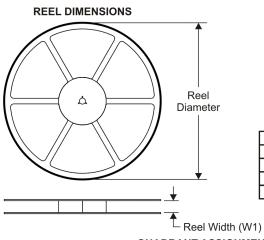

#### TAPE AND REEL INFORMATION

# TAPE DIMENSIONS + K0 - P1 - B0 W Cavity - A0 -

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

|    | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

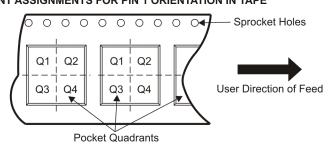

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

\*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|---------|---------|---------|------------|-----------|------------------|

| INA203AIDGSR | MSOP            | DGS                | 10 | 2500 | 330.0                    | 12.4                     | 5.3     | 3.4     | 1.4     | 8.0        | 12.0      | Q1               |

| INA203AIDGST | MSOP            | DGS                | 10 | 250  | 180.0                    | 12.4                     | 5.3     | 3.4     | 1.4     | 8.0        | 12.0      | Q1               |

| INA203AIDR   | SOIC            | D                  | 14 | 2500 | 330.0                    | 16.4                     | 6.5     | 9.0     | 2.1     | 8.0        | 16.0      | Q1               |

| INA203AIPWR  | TSSOP           | PW                 | 14 | 2000 | 330.0                    | 12.4                     | 7.0     | 5.6     | 1.6     | 8.0        | 12.0      | Q1               |

| INA204AIDGSR | MSOP            | DGS                | 10 | 2500 | 330.0                    | 12.4                     | 5.3     | 3.4     | 1.4     | 8.0        | 12.0      | Q1               |

| INA204AIDGST | MSOP            | DGS                | 10 | 250  | 180.0                    | 12.4                     | 5.3     | 3.4     | 1.4     | 8.0        | 12.0      | Q1               |

| INA204AIDR   | SOIC            | D                  | 14 | 2500 | 330.0                    | 16.4                     | 6.5     | 9.0     | 2.1     | 8.0        | 16.0      | Q1               |

| INA204AIPWR  | TSSOP           | PW                 | 14 | 2000 | 330.0                    | 12.4                     | 7.0     | 5.6     | 1.6     | 8.0        | 12.0      | Q1               |

| INA205AIDGSR | MSOP            | DGS                | 10 | 2500 | 330.0                    | 12.4                     | 5.3     | 3.4     | 1.4     | 8.0        | 12.0      | Q1               |

| INA205AIDGST | MSOP            | DGS                | 10 | 250  | 180.0                    | 12.4                     | 5.3     | 3.4     | 1.4     | 8.0        | 12.0      | Q1               |

| INA205AIDR   | SOIC            | D                  | 14 | 2500 | 330.0                    | 16.4                     | 6.5     | 9.0     | 2.1     | 8.0        | 16.0      | Q1               |

| INA205AIPWR  | TSSOP           | PW                 | 14 | 2000 | 330.0                    | 12.4                     | 7.0     | 5.6     | 1.6     | 8.0        | 12.0      | Q1               |

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| INA203AIDGSR | MSOP         | DGS             | 10   | 2500 | 346.0       | 346.0      | 29.0        |

| INA203AIDGST | MSOP         | DGS             | 10   | 250  | 184.0       | 184.0      | 50.0        |

| INA203AIDR   | SOIC         | D               | 14   | 2500 | 346.0       | 346.0      | 33.0        |

| INA203AIPWR  | TSSOP        | PW              | 14   | 2000 | 346.0       | 346.0      | 29.0        |

| INA204AIDGSR | MSOP         | DGS             | 10   | 2500 | 346.0       | 346.0      | 29.0        |

| INA204AIDGST | MSOP         | DGS             | 10   | 250  | 184.0       | 184.0      | 50.0        |

| INA204AIDR   | SOIC         | D               | 14   | 2500 | 346.0       | 346.0      | 33.0        |

| INA204AIPWR  | TSSOP        | PW              | 14   | 2000 | 346.0       | 346.0      | 29.0        |

| INA205AIDGSR | MSOP         | DGS             | 10   | 2500 | 346.0       | 346.0      | 29.0        |

| INA205AIDGST | MSOP         | DGS             | 10   | 250  | 184.0       | 184.0      | 50.0        |

| INA205AIDR   | SOIC         | D               | 14   | 2500 | 346.0       | 346.0      | 33.0        |

| INA205AIPWR  | TSSOP        | PW              | 14   | 2000 | 346.0       | 346.0      | 29.0        |

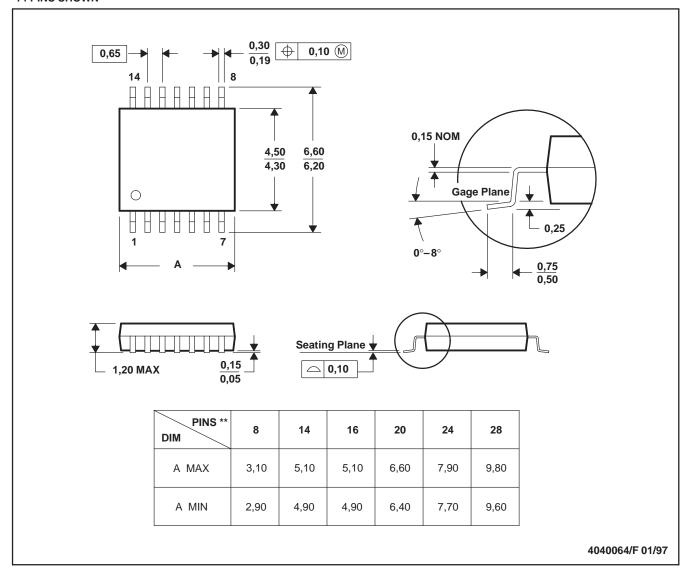

#### PW (R-PDSO-G\*\*)

#### 14 PINS SHOWN

#### PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

D. Falls within JEDEC MO-153

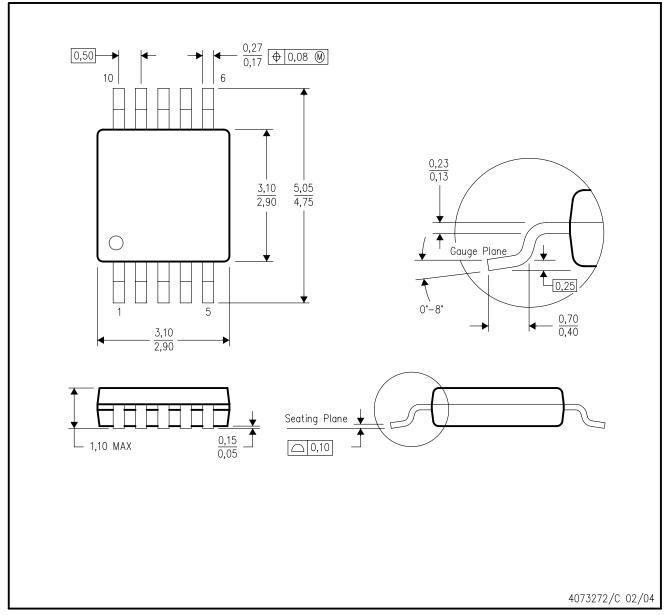

## DGS (S-PDSO-G10)

#### PLASTIC SMALL-OUTLINE PACKAGE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion.

- D. Falls within JEDEC MO-187 variation BA.

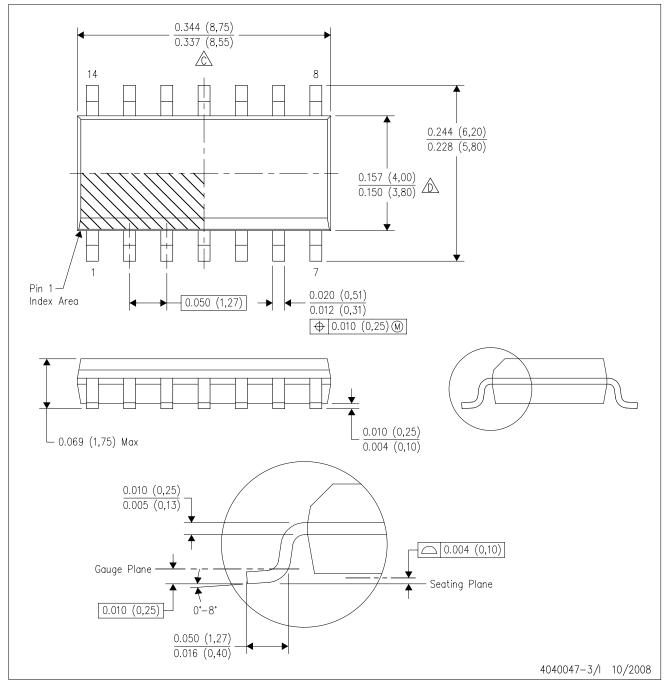

### D (R-PDSO-G14)

#### PLASTIC SMALL-OUTLINE PACKAGE

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 (0,15) per end.

- Body width does not include interlead flash. Interlead flash shall not exceed .017 (0,43) per side.

- E. Reference JEDEC MS-012 variation AB.