## Primary Side Quasi-Resonant BJT Controller

## with CV/CC Operation

#### **REV: P00**

The values contained in this preliminary datasheet are for reference only. Users should verify for a current and complete document before placing orders.

### **General Description**

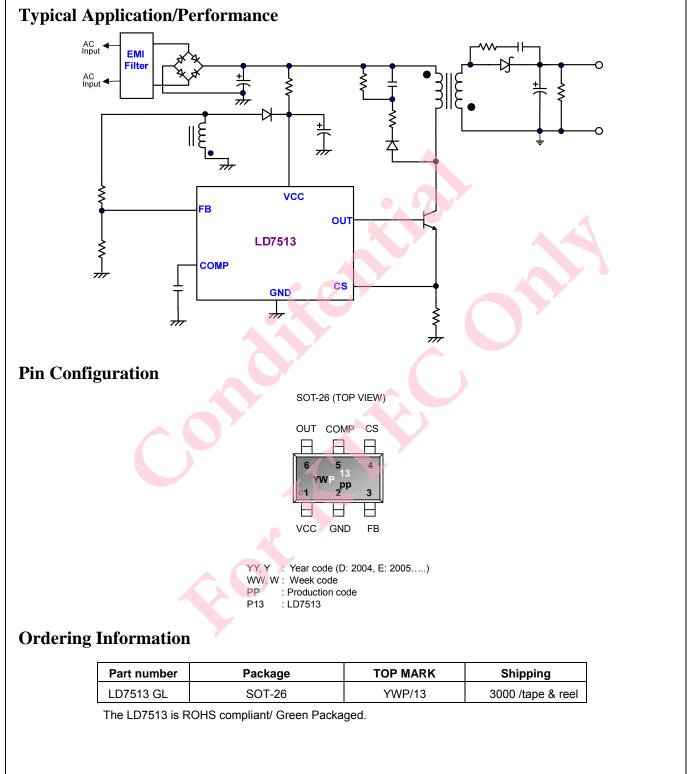

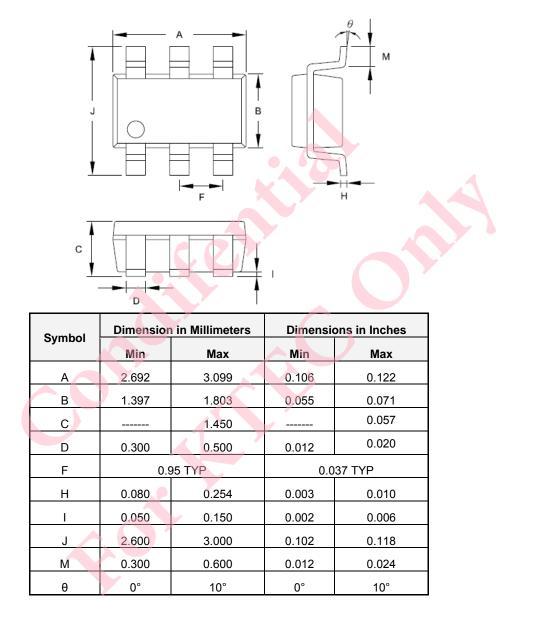

The LD7513 is an excellent primary side feedback BJT controller with CV/CC operation, integrated with several functions of protections. It minimizes the components counts and is available in a tiny SOT-26 package. Those make it an ideal design for low cost applications.

It provides functions of ultra-low startup current, green-mode power-saving operation and leading-edge blanking of the current sensing. Also, the LD7513 features Internal OTP (Over Temperature Protection) and OVP (Over Voltage Protection) to prevent the circuit from being damaged due to abnormal conditions.

In most cases, the power supply with primary-side feedback controller would accompany with some serious load regulation effect. To deal with this problem, the LD7513 consists of dedicated load regulation compensation circuit to enhance its performance.

#### Features

- Primary-Side Feedback Control With Quasi-Resonant

Operation

- Direct Drive Of BJT Switch

- Built-In Load Regulation Compensation

- Constant Current Control

- Ultra-Low Startup Current (<1.3µA)</li>

- 0.5mA Low Operating Current at Light Load

- 75 kHz Maximum Switching Frequency.

- Current Mode Control

- Green Mode Control Improve Efficiency

- LEB (Leading-Edge Blanking) On CS Pin

- Built-in Soft Start

- VCC OVP (Over Voltage Protection)

- FB Pin Open/Short Protection

- Internal OTP (Over Temperature Protection)

### Applications

- Mobile Phone Charger

- Lower Power AC/DC Adaptor

### **Pin Descriptions**

| NAME | PIN | FUNCTION                                                |  |

|------|-----|---------------------------------------------------------|--|

| VCC  | 1   | upply voltage pin.                                      |  |

| GND  | 2   | bund.                                                   |  |

| FB   | 3   | Auxiliary voltage sense and Quasi Resonant detection.   |  |

| CS   | 4   | Current sense pin, connect to sense the Switch current. |  |

| COMP | 5   | Output of the error amplifier for voltage compensation. |  |

| OUT  | 6   | Base drive output to drive the external BJT Switch.     |  |

## **Block Diagram**

3

## **Absolute Maximum Ratings**

| Supply Voltage VCC,                                       | 20V            |

|-----------------------------------------------------------|----------------|

| OUT                                                       | -0.3 ~3.3V     |

| COMP, FB, CS                                              | -0.3 ~3.3V     |

| Maximum Junction Temperature                              | 150°C          |

| Storage Temperature Range                                 | -65°C to 150°C |

| Package Thermal Resistance (SOT-26, $\theta_{JA}$ )       | 200°C/W        |

| Power Dissipation (SOT-26, at Ambient Temperature = 85°C) | 200mW          |

| Lead temperature (Soldering, 10sec)                       | 260°C          |

| ESD Voltage Protection, Human Body Model                  | 2.5 KV         |

| ESD Voltage Protection, Machine Model                     | 250 V          |

#### Caution:

Stress exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stress above Recommended Operating Conditions may affect device reliability.

### **Recommended Operating Conditions**

| Item                                         | Min. | Max. | Unit |

|----------------------------------------------|------|------|------|

| Operating Ambient Temperature                | -40  | 85   | °C   |

| Operating Junction Temperature               | -40  | 125  | °C   |

| Supply VCC Voltage                           | 4.8  | 16   | V    |

| VCC Capacitor                                | 0.68 | 4.7  | μF   |

| Start-up resistor Value (AC Side, Half Wave) | 1M   | 6.6M | Ω    |

| Comp Pin Capacitor                           | 330  | 2200 | pF   |

Note:

- It's essential to connect VCC pin with a SMD ceramic capacitor (0.1μF~0.47μF) to filter out the undesired switching noise for stable operation. This capacitor should be placed close to IC pin as possible

- 2. Connecting a capacitor to COMP pin is also essential to filter out the undesired switching noise for stable operation.

- 3. The small signal components should be placed to IC pin as possible.

## **Electrical Characteristics**

$(T_A = +25^{\circ}C \text{ unless otherwise stated}, V_{CC}=12.0V)$

| PARAMETER                                   | CONDITIONS                               | MIN   | TYP  | MAX   | UNITS |

|---------------------------------------------|------------------------------------------|-------|------|-------|-------|

| Supply Voltage (Vcc Pin)                    |                                          |       |      |       |       |

| Startup Current                             | VCC=UVLO-ON-0.05V                        |       | 0.8  | 1.3   | μA    |

|                                             | V <sub>COMP</sub> =0V, OUT= open, FB=2V  |       | 0.5  |       | mA    |

| Operating Current                           | V <sub>COMP</sub> =2.5V, OUT=open, FB=2V |       | 0.55 |       | mA    |

|                                             | OVP/ZCD UVP tripped, FB=0V               |       | 0.25 |       | mA    |

| UVLO (off)                                  |                                          | 3.4   | 4.0  | 4.6   | V     |

| UVLO (on)                                   |                                          | 5     | 12   |       | V     |

| Vcc OVP Level                               |                                          |       | 18   |       | V     |

| Vcc OVP De-bounce time                      | *                                        |       | 64   |       | μs    |

| Error Amplifier (COMP pin)                  |                                          |       |      |       |       |

| Reference Voltage, V <sub>REF</sub>         |                                          | 1.98  | 2.00 | 2.02  | V     |

| Transconductance                            |                                          |       | 80   |       | μmho  |

|                                             | V <sub>FB</sub> = Vref+0.05, Vcomp=2V    |       | -4   |       | μA    |

| Output Sink Current                         | V <sub>FB</sub> =2.6V                    |       | -80  |       | μA    |

|                                             | V <sub>FB</sub> = Vref-0.05V, Vcomp=2V   |       | 4    |       | μA    |

| Output Source Current                       | V <sub>FB</sub> =1.4V                    |       | 80   |       | μA    |

| Output Upper Clamp Voltage                  | V <sub>FB</sub> =1V                      | 2.7   | 3    | 3.3   | V     |

| Load Compensation Current                   | V <sub>COMP</sub> =3V                    |       | 10   |       | μA    |

| Current Sensing (CS Pin)                    |                                          |       |      |       |       |

| Maximum Input Voltage, V <sub>CS(OFF)</sub> |                                          | 0.9   | 1    | 1.1   | V     |

| Minimum V <sub>CS-OF</sub>                  | V <sub>COMP</sub> < 0.45V                | 0.135 | 0.15 | 0.165 | V     |

| Leading Edge Blanking Time                  |                                          |       | 525  |       | ns    |

| Input impedance                             |                                          | 1     |      |       | MΩ    |

| Delay to Output                             | *                                        |       | 100  |       | ns    |

| QRD (Quasi Resonant Detection, I            | FB Pin)                                  |       |      |       |       |

| Lower Clamp Voltage                         | I <sub>DET</sub> =-1mA*                  |       | -0.3 |       | V     |

|                                             |                                          |       | 100  |       | mV    |

| QRD Trip Level                              | Hysteresis                               |       | 100  |       | mV    |

| QR Mode Time Out 1                          |                                          |       | 6    |       | μS    |

\*: Guaranteed by design.

| PARAMETER                          | CONDITIONS                      | MIN | ТҮР | MAX | UNITS |

|------------------------------------|---------------------------------|-----|-----|-----|-------|

|                                    | After soft start                |     | 4   |     | ms    |

| Max Frequency Clamp Time Out 2     | During soft start*              |     | 80  |     | μs    |

| QR Mode Blanking Time              |                                 |     | 1   |     | μS    |

| Input Bias Current                 | V <sub>FB</sub> =1V~5V, OUT=OFF | 0.0 |     | 1.0 | μA    |

| Oscillator for Switching Frequency | ,                               |     |     |     |       |

| Maximum Frequency                  |                                 |     | 75  |     | kHz   |

| Green Mode Frequency               |                                 |     | 25  |     | kHz   |

| Minimum Frequency                  |                                 |     | 1.4 |     | kHz   |

| Maximum ON Time                    |                                 |     |     |     |       |

| Maximum On Time                    |                                 |     | 13  |     | μs    |

| Output Drive (OUT Pin)             |                                 |     |     |     |       |

| Output Low ON-resistance           | I <sub>SINK</sub> =50mA         |     | 2.5 |     | Ω     |

| Max. Output Base Current           | VCS=1V                          |     | 30  |     | mA    |

| Soft Start                         |                                 |     |     |     |       |

| Soft Start Time                    | *                               |     | 5   |     | ms    |

| FB Under Voltage Protection (UVP   | , FB Pin)                       |     |     |     |       |

| Under Voltage Level                |                                 |     | 0.5 |     | V     |

|                                    | After soft start*               |     | 10  |     | ms    |

| UVP Delay Time                     | At start-up                     |     | 15  |     | ms    |

| C.C. Disable Level                 |                                 |     | 1.0 |     | V     |

| On Chip OTP (Over Temperature)     |                                 |     |     |     |       |

| OTP Level                          | *                               |     | 140 |     | °C    |

| OTP Hysteresis                     | *                               |     | 10  |     | °C    |

\*: Guaranteed by design.

### **Application Information**

### **Operation Overview**

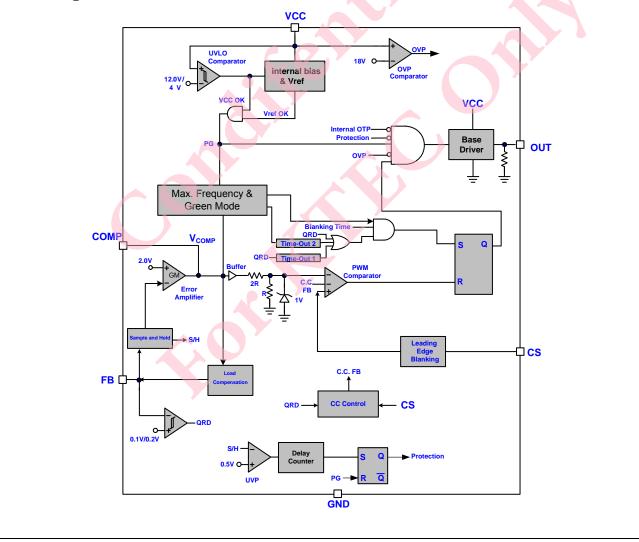

The LD7513 is an excellent primary side feedback controller with Quasi-Resonant operation to provide high efficiency and better EMI performance. The LD7513 removes the need for secondary feedback circuits while achieving excellent line and load regulation. It meets the green-power requirement and is intended for the use in those modern switching power suppliers and linear adaptors that demand higher power efficiency and power-saving. It integrates with more functions to reduce the external components counts and the size. Its major features are described as below.

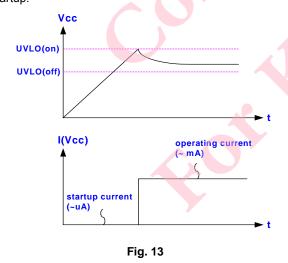

### Under Voltage Lockout (UVLO)

An UVLO comparator is implemented in it to detect the voltage across VCC pin. It would assure the supply voltage enough to turn on the LD7513 PWM controllers and further to drive the power BJT. As shown in Fig. 13, a hysteresis is built in to prevent shutdown from voltage dip during startup.

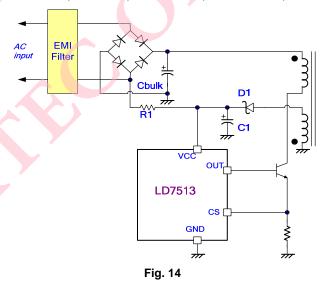

## Startup Current and Startup Circuit

The typical startup circuit to generate VCC of the LD7513 is shown in Fig. 14. During startup transient, the VCC sinks

below the UVLO threshold, so there's no pulse delivering out from LD7513 to drive the power BJT. Therefore, the current through R1 will be used to charge the capacitor C1. Until the VCC is fully charged to enable the LD7513 to deliver the drive-out signal, the auxiliary winding will provide the supply current instead. If PWM controller requires less current to start up, it will allow less power consumption on R1. By using CMOS process and some unique circuit design, the LD7513 requires only  $1.3\mu$ A max to start up. Higher resistance of R1 will spend much more time to start up. The user is recommended to select proper value of R1 and C1 to optimize the power consumption and startup time.

### **Principle of CV Operation**

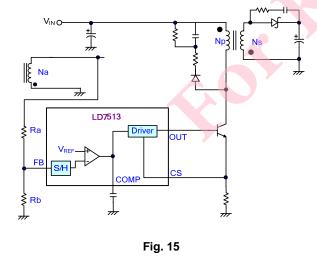

In the DCM flyback converter, it senses the output voltage by auxiliary winding. LD7513 samples the auxiliary winding on the primary-side to regulate the output voltage, as shown in the Fig. 15. The voltage induced in the auxiliary winding is a reflection of the secondary winding voltage while the BJT is in off state. Via a resistor divider connected between the auxiliary winding and FB pin, the auxiliary voltage is

sampled after the sample delay time and will be hold until the next sampling. The sampled voltage is compared with internal reference  $V_{REF}$  (2.0V) and the error will be amplified. The error amplifier output COMP reflects the load condition and controls the duty cycle to regulate the output voltage, thus constant output voltage can be achieved. The output voltage is given as:

$$V_{OUT} = 2.0V(1 + \frac{Ra}{Rb})(\frac{Ns}{Na}) - V_F$$

Where  $V_F$  indicates the drop voltage of the output Diode, Ra and Rb are top and bottom feedback resistor value, Ns and Na are the turns of transformer secondary and auxiliary.

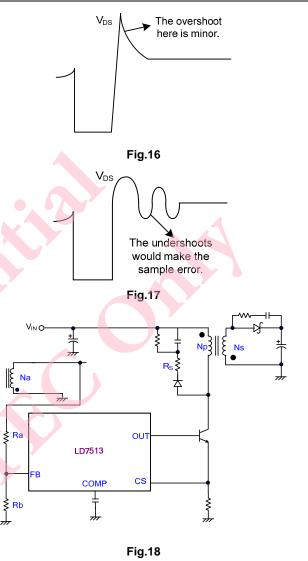

In case that the output voltage is sensed through the auxiliary winding; the leakage inductance will induce ringing to affect output regulation. To optimize the drain voltage clamp circuit will minimize the high frequency ringing and achieve the best regulation. Fig. 16 shows the desired drain voltage waveform in compare to those with large undershoot due to leakage inductance induced ring (Fig. 17). This will make the sample error and cause poor performance for output voltage regulation. A proper selection for resistor RS, in series with the clamp diode, may reduce any large undershoot, as shown in Fig. 18.

#### Load Regulation Compensation

8

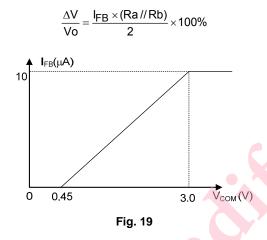

LD7513 implemented with load regulation compensation to compensate the cable voltage droop and to achieve a better voltage regulation. The offset voltage is created across FB by an internal sink current source which feeds out the FB during the sampling period. The internal sink current source is proportional to the value of  $V_{COMP}$ , as shown in Fig. 19. As a result, the drop due to the cable loss can be compensated. So that, the offset voltage decreases as the Vcomp

decrease in condition from full-load to no-load. It can also be programmed by adjusting the resistance of the divider to compensate the drop for various cable lines used. The equation of internal sink current source is shown as:

$I_{FB} \cong (V_{COMP} - 0.45) * 3.92 \quad (\mu A)$

The percentage of maximum compensation is shown as:

#### **Quasi-Resonant Mode Detection**

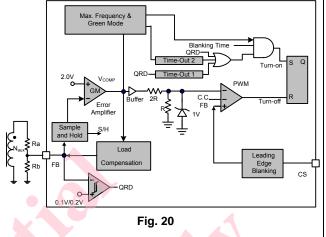

The LD7513 employs quasi-resonant (QR) switching scheme to switch valley-mode either in CV or CC operation. This property feature greatly reduces the switching loss and dv/dt in the entire operating range for the power supply. Fig. 20 shows the typical QR detection block. The QR detection block will detect auxiliary winding signal to drive BJT as FB pin voltage drops to 0.1V. The QR comparator would not operate if FB pin voltage remains above 0.2V. The 4ms of time-out2 generates a BJT turn-on signal as the driver output drops to low level for more than 4ms with the falling edge of the driver output.

### Multi-Mode Operation

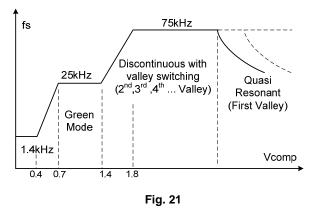

The LD7513 is a QR controller operating in multi-modes. The controller changes operation modes according to line voltage and load conditions. At heavy-load ( $V_{COMP}$ >1.8V, Fig. 21), there might be two situations to meet. If the system AC input is in low line, the LD7513 will turn on in first valley. If in high line, the switching frequency will increase till over the clamp of 75KHZ and skip the first valley to turn on in 2<sup>nd</sup> valley. The switching frequency would vary depending on the line voltage and the load conditions when the system is operated in QR mode.

At medium or light load conditions ( $1.4V < V_{COMP} < 1.8V$ , Fig. 15), the frequency clamp is reduced to 25 kHz maximum as  $V_{COMP}$  down to  $V_{SG1}$ . However, the valley switching characteristic behaves as well in these conditions. The LD7513 will jump to turn on in 3<sup>rd</sup>, 4<sup>th</sup>.... valley. That is, when load decreases, the system automatically skip more valleys and the switching frequency is thus reduced. In such way, a smooth frequency fold back is realized and high power efficiency is achieved.

At zero load or very light load conditions ( $V_{COMP}$ <0.7), the system operates in green mode for power saving. In green mode, the system modulates the frequency according to the

load and  $V_{\text{COMP}}$  conditions. Once  $V_{\text{COMP}}$  is lower than  $V_{\text{SG2}},$  the switching frequency starts to linearly decrease from 25 kHz to 1.4 kHz.

### Current Sensing and Leading-edge Blanking

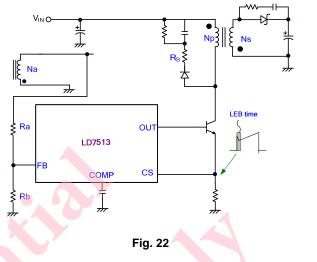

The typical current mode of PWM controller feedbacks both current signal and voltage signal to close the control loop and achieve regulation. As shown in Fig. 22, the LD7513 detects the primary BJT current from the CS pin, which is not only for the peak current mode control but also for the pulse-by-pulse current limit. The maximum voltage threshold of the current sensing pin is set at 1V. From above, the BJT peak current can be obtained from below.

$$I_{\text{PEAK}(\text{MAX})} = \frac{1V}{R_{\text{S}}}$$

A leading-edge blanking (LEB) time is included in the input of CS pin to prevent the false-trigger from the current spike.

### Principle of C.C. Operation

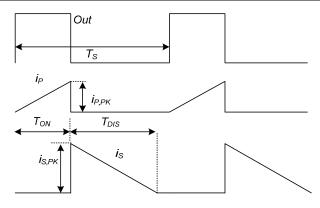

The primary side control scheme is applied to eliminate secondary feedback circuit or opto-coupler, which will reduce the system cost. The switching waveforms are shown in Fig. 23. The output current lo can be expressed as:

$$o = \frac{1}{2} \frac{i_{S,PK} \times T_{DIS}}{T_S}$$

$$= \frac{1}{2} \frac{N_P}{N_S} \times i_{P,PK} \times \frac{T_{DIS}}{T_S}$$

$$= \frac{1}{2} \frac{N_P}{N_S} \times \frac{V_{CS}}{R_S} \times \frac{T_{DIS}}{T_S}$$

The primary peak current  $i_{P,PK}$ , inductor current discharge time ( $T_{DIS}$ ) and switching period ( $T_S$ ) can be detected by the IC. The ratio of  $V_{CS^*}T_{DIS}/T_S$  will be modulated as a constant ( $V_{CS^*}T_{DIS}/T_S = 1/3$ ). I<sub>O</sub> can be induced finally by

$$\begin{split} \text{Io} &\cong \frac{1}{2} \frac{\text{Np}}{\text{N}_S} \times \frac{\text{V}_{CS}}{\text{R}_S} \times \frac{\text{T}_{DIS}}{\text{T}_S} \\ &\cong \frac{1}{2} \frac{\text{Np}}{\text{N}_S} \times \frac{1}{\text{R}_S} \times \frac{1}{3} \end{split}$$

However this is an approximate equation. The user may fine-tune it according to the experiment result.

10

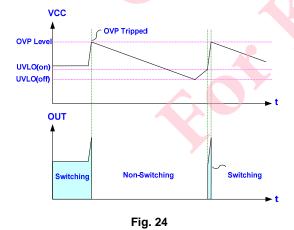

### OVP (Over Voltage Protection) on Vcc - Auto

### Recovery

LD7513 is implemented with OVP function over Vcc. As the Vcc voltage rises over the OVP threshold voltage, the output drive circuit will be shutdown simultaneously thus to stop the switching of the power BJT until the next UVLO(on) arrives. The Vcc OVP function of LD7513 is an auto-recovery type protection. The Fig. 24 shows its operation. On the other hand, if the OVP condition is removed, the Vcc level will get back to normal level and the output will automatically return to the normal operation.

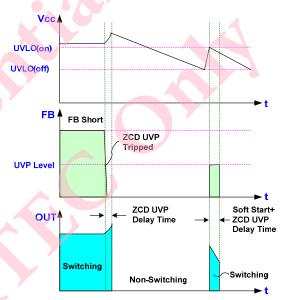

### FB Under Voltage Protection (FB UVP) – Auto Recovery

LD7513 is implemented with an UVP function over FB pin. If the FB voltage falls below 0.5V for over the delay time of FB UVP, the protection will be activated to stop the switching of the power BJT until the next UVLO(on) arrives. The FB UVP function in LD7513 is an auto-recovery type protection. The Fig. 25 shows its operation. The FB UVP is disabled during the soft start.

Fig. 25

Package Information SOT-26

#### **Important Notice**

Leadtrend Technology Corp. reserves the right to make changes or corrections to its products at any time without notice. Customers should verify the datasheets are current and complete before placing order.

13

## **Revision History**

| Rev. | Date      | Change Notice                  |

|------|-----------|--------------------------------|

| P00  | 3/15/2013 | Preliminary Specification.     |

|      |           | 將 Fig 20 的 Vref 由 2.5 修正為 2.0V |