#### **New Product**

# High Performance Step-Down DC-DC Converter With Dynamically Adjustable Output Voltage

#### **FEATURES**

- 2-MHz PWM Operation

- Integrated MOSFET Switches

- 2.6-V to 6.0-V Input Voltage Range

- Minimal Number of External Components

- Up to 96% conversion efficiency

- 600-mA Load Capability

- 100% Duty Cycle Allows Low Dropout

- Integrated Compensation Circuit

- Over-Current Protection

- Shutdown Current < 2 μA</li>

- Thermal Shutdown

- Integrated UVLO

- 10-Pin MSOP and Space Saving MLP33 Packaging

- DAC Input for Dynamic Output Voltage Adjustment

- Synchronizable to13-MHz Clock

- User Selectable PWM, PSM, or AUTO Mode

- PSM Frequency ≥ 20 kHz for Inaudible Harmonics

#### **APPLICATIONS**

- W-CDMA Cell Phone

- PDAs/Palmtop PCs

- LCD Modules

- Portable Image Scanners

- GPS Receivers

- Smart Phones

- MP3 Players

- 3G Cell Phone

- Digital Cameras

#### **DESCRIPTION**

The Si9174 is a high efficiency 600-mA step down converter with internal low on resistance power MOSFET switch and synchronous rectifier transistors. It is designed to convert one cell Lilon battery or three cell alkaline battery voltages to a dynamically adjustable dc output. The voltage on the DAC pin controls the output voltage. The output voltage is adjustable between 0.4 V and the input voltage  $V_{\mbox{\scriptsize IN}}$  less a small dropout voltage and settles in <30  $\mu s$ .

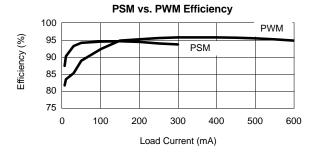

In order to insure efficient conversion throughout the entire load range, PWM (pulse width modulation), PSM (pulse skipping mode) or Auto mode can be selected. In PWM mode, 2-MHz switching permits use of small external inductor and

capacitor sizes allowing *one of the smallest solutions*. To minimize system noise, the switching frequency can be synchronized to an external 13-MHz clock.

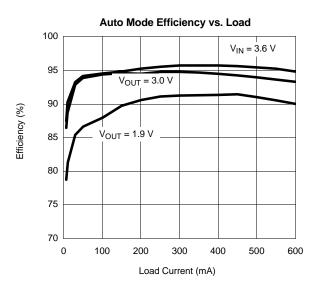

PSM mode provides increased efficiency at light loads. In PSM mode the oscillator frequency is kept above 20 kHz to avoid audio band interference. When operating in Auto mode, the converter automatically selects operating in either PWM or PSM mode according to load current demand.

The Si9174 is available in 10-pin MSOP and even smaller MLP33 packages and is specified to operate over the industrial temperature range of -40°C to 85°C.

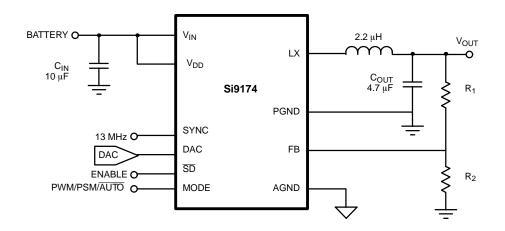

#### TYPICAL APPLICATIONS CIRCUIT

#### **New Product**

#### **ABSOLUTE MAXIMUM RATINGS**

| 6.2 V                                      |

|--------------------------------------------|

| -0.3 to 6.2 V                              |

| (or to $V_{DD}$ + 0.3 V whichever is less) |

| 0.3 to +0.3 V                              |

| 2 kV                                       |

| 65 to 125°C                                |

| 150°C                                      |

|                                            |

| 481 mW                                     |

| 915 mW                                     |

|                                            |

| Thermal Impedance ( $\Theta_{JA}$ )                            |       |

|----------------------------------------------------------------|-------|

| 10-Pin MSOP                                                    | 5°C/W |

| 10-Pin MLP33                                                   | °C/W  |

| Peak Inductor Current                                          | 1.8 A |

| Notes                                                          |       |

| a Device mounted with all leads soldered or welded to PC board |       |

- b. Derate 7.4 mW/°C above 85°C.

- c. Derate 14 mW/°C above 85°C.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **RECOMMENDED OPERATING RANGE**

| V <sub>IN</sub> Range         | Inductor                                    |

|-------------------------------|---------------------------------------------|

| C <sub>IN</sub> 10 μF Ceramic | Operating Load Current PWM Mode 0 to 600 mA |

| $C_{OUT}$ 4.7 $\mu F$ Ceramic | Operating Load Current PSM Mode 0 to 150 mA |

| SPECIFICATION                | <b>VS</b>         |                    |                                                                                                                                   |                    |                         |                  |                         |                  |

|------------------------------|-------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------|------------------|-------------------------|------------------|

| Parameter                    |                   |                    | Test Conditions Unless                                                                                                            | Specified          |                         | Limits           |                         |                  |

|                              | Mode <sup>f</sup> | Symbol             | -40 °C to 85°C, $V_{IN} = V_{DD}$ , $V_{DAC} = 1.2$ °C <sub>OUT</sub> = 4.7 μF, L = 2.2 μH, 2.6 V ≤ $R_1 = 11.3$ kΩ, $R_2 = 20$ k | Min <sup>a</sup>   | Typb                    | Max <sup>a</sup> | Unit                    |                  |

| Under Voltage Lock           | out (UVL          | O)                 |                                                                                                                                   |                    | •                       |                  | •                       |                  |

| Under Voltage Lockout (tu    | rn-on)            |                    | V <sub>IN</sub> rising                                                                                                            |                    | 2.3                     |                  | 2.5                     | .,               |

| Hysteresis                   |                   |                    |                                                                                                                                   |                    |                         | 0.1              |                         | V                |

| Shutdown (SD)                |                   |                    |                                                                                                                                   |                    |                         |                  |                         |                  |

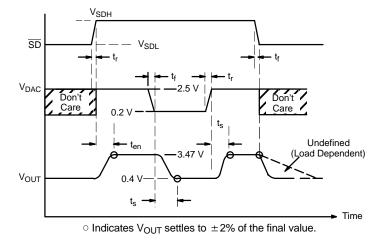

| Logic HIGH                   |                   | V <sub>SDH</sub>   |                                                                                                                                   |                    | 1.6                     |                  |                         | .,               |

| Logic LOW                    |                   | V <sub>SDL</sub>   |                                                                                                                                   |                    |                         |                  | 0.4                     | V                |

| Delevite Output              |                   |                    | Settle Within ±2% accuracy SD rising                                                                                              | $R_L = 3.3 \Omega$ |                         |                  | 100                     |                  |

| Delay to Output <sup>c</sup> |                   | t <sub>en</sub>    | t <sub>r</sub> < 1 μs                                                                                                             | $R_L = 51 \Omega$  |                         | 100              |                         | μS               |

| Pull Down                    |                   | I <sub>SD</sub>    | Input at V <sub>IN</sub>                                                                                                          |                    |                         |                  | μΑ                      |                  |

| Mode Selection Tri-          | Level Log         | ic (MODE)          |                                                                                                                                   |                    |                         |                  |                         |                  |

| MODE Pin HIGH                | PWM               |                    |                                                                                                                                   |                    | V <sub>IN</sub> -0.4    | V <sub>IN</sub>  |                         | V                |

| MODE Pin LOW                 | Auto              |                    |                                                                                                                                   |                    |                         |                  | 0.4                     | V                |

| Mode Pin Input Current       |                   |                    | MODE = GND                                                                                                                        |                    |                         | -5               |                         | μΑ               |

| Mode Pin Input Current       |                   |                    | $MODE = V_{IN}$                                                                                                                   |                    |                         | 5                |                         | μΑ               |

| Oscillator                   |                   |                    |                                                                                                                                   |                    |                         |                  |                         |                  |

| Frequency f <sub>O</sub>     |                   | fosc               |                                                                                                                                   |                    | 1.6                     | 2                | 2.4                     | MHz              |

| External Clock Syn           | chronizati        | on (SYNC)          |                                                                                                                                   |                    |                         |                  |                         |                  |

| Frequency                    |                   |                    | SYNC Input = 500 mV <sub>p-p</sub>                                                                                                |                    |                         | 13               |                         | MHz              |

| Ac Coupled Sinewave          |                   |                    | Frequency = 13 MHz                                                                                                                |                    | 0.2                     |                  | 0.8                     | V <sub>p-p</sub> |

| Error Amplifier (FB,         | DAC Pin)          |                    |                                                                                                                                   |                    |                         |                  |                         |                  |

| FB Voltage Accuracy          |                   |                    |                                                                                                                                   |                    | V <sub>DAC</sub><br>-20 |                  | V <sub>DAC</sub><br>+20 | mV               |

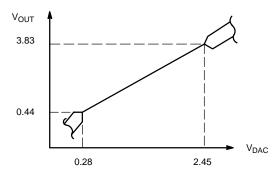

| DAC Input Voltage Range      |                   |                    | V <sub>IN</sub> > 2.6, V <sub>IN -</sub> V <sub>DAC</sub> > 0                                                                     | .5 V               | 0.28                    |                  | 2.45                    | V                |

| Input Bias Current FB, DA    | С                 | I <sub>FBDAC</sub> | V <sub>FB</sub> = 1.25 V                                                                                                          |                    | -1                      | 0.01             | 1                       | μΑ               |

#### **New Product**

### Vishay Siliconix

| <b>SPECIFICATIO</b>                     | NS                   |                                         |                                                                                                                                                                                                               |                                         |                           |                  |      |                  |                   |

|-----------------------------------------|----------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------------|------------------|------|------------------|-------------------|

| Parameter                               |                      |                                         | Test Conditions Unless Specified                                                                                                                                                                              |                                         | Limits                    |                  |      |                  |                   |

|                                         | Mode <sup>f</sup>    | Symbol                                  | -40 °C to 85°C, $V_{\text{IN}}$ = $V_{\text{DD,}}$ $V_{\text{DAC}}$ = 1.215 V, $C_{\text{IN}}$ = 10 μF, $C_{\text{OUT}}$ = 4.7 μF, L = 2.2 μH, 2.6 V ≤ $V_{\text{IN}}$ ≤ 5.5 V $R_1$ = 11.3 kΩ, $R_2$ = 20 kΩ |                                         |                           | Min <sup>a</sup> | Typb | Max <sup>a</sup> | Unit              |

| <b>Converter Operation</b>              | on                   |                                         |                                                                                                                                                                                                               |                                         |                           |                  |      |                  |                   |

| Maximum Output<br>Current               | PWM                  | I <sub>LOAD</sub>                       | V <sub>IN</sub> =                                                                                                                                                                                             | 3.6 V                                   |                           | 600              |      |                  | mA                |

| Maximum Output<br>Current               | PSM                  | I <sub>LOAD</sub>                       | V <sub>IN</sub> =                                                                                                                                                                                             | 3.6 V                                   |                           |                  |      | 150              | mA                |

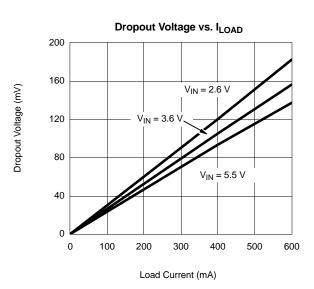

| Dropout Voltagee                        |                      | $V_{DD}$                                | $V_{IN} = 2.6 \text{ V}, I_{C}$                                                                                                                                                                               | <sub>DUT</sub> = 600                    | mA                        |                  | 190  | 300              | mV                |

| Closed Loop Bandwidth                   |                      | BW                                      |                                                                                                                                                                                                               |                                         |                           |                  | 300  |                  | kHz               |

| Load DegulationC                        | PWM                  |                                         | V <sub>IN</sub> = 3.6 V<br>V <sub>OUT</sub> = 1.9 V @ 25°C                                                                                                                                                    | I <sub>OUT</sub> =                      | 30 mA to 600 mA           |                  | 0.5  |                  | - %               |

| Load Regulation <sup>c</sup>            | PSM                  |                                         | V <sub>OUT</sub> = 1.9 V @ 25°C                                                                                                                                                                               | I <sub>OUT</sub> =                      | 30 mA to 75 mA            |                  | 0.25 |                  | %                 |

| Line Demoleties                         | PWM                  |                                         | V 20VV                                                                                                                                                                                                        | 0.5.1/4                                 |                           |                  | ±0.1 |                  | %/V               |

| Line Regulation                         | PSM                  |                                         | $V_{OUT} = 3.0 \text{ V}, V_{II}$                                                                                                                                                                             | $_{1} = 3.5 \text{ V tc}$               | ) 5.5 V                   |                  | ±0.1 |                  |                   |

| PWM/PSM Switch Thresh                   | nold Current         | I <sub>AUpk</sub>                       |                                                                                                                                                                                                               |                                         |                           |                  | 200  |                  |                   |

| Maximum Inductor Peak                   | Current Limit        | I <sub>Lpk</sub>                        |                                                                                                                                                                                                               |                                         |                           |                  | 1500 |                  | mA                |

| Maximum NMOS<br>Transistor Current Sink | PWM                  |                                         | Negative Tran                                                                                                                                                                                                 | Negative Transition on V <sub>DAC</sub> |                           |                  |      |                  | 1 11/5            |

|                                         | P-Channel            |                                         |                                                                                                                                                                                                               |                                         | 250                       |                  |      |                  |                   |

| On Resistance                           | N-Channel            | r <sub>DS(on)</sub>                     | V <sub>IN</sub> =                                                                                                                                                                                             | 3.6 V                                   |                           |                  | 250  |                  | mΩ                |

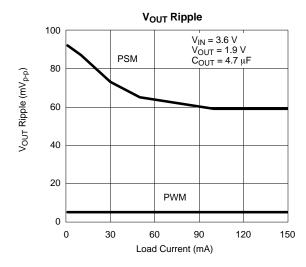

| 0                                       | PWM                  |                                         | 0.07.0.0                                                                                                                                                                                                      |                                         | I <sub>OUT</sub> = 600 mA |                  | 60   |                  | .,                |

| Output Ripple Voltage                   | PSM                  |                                         | $0.05~\Omega~C_{\text{OUT(ESR)}}$                                                                                                                                                                             |                                         | I <sub>OUT</sub> = 30 mA  |                  | 80   |                  | mV <sub>p-p</sub> |

|                                         | PWM                  |                                         |                                                                                                                                                                                                               |                                         | I <sub>OUT</sub> = 600 mA |                  | 90   |                  |                   |

| Efficiency                              | PSM                  |                                         | $V_{IN} = 3.6 \text{ V}, V_{OUT} = 3.3$                                                                                                                                                                       | V                                       | I <sub>OUT</sub> = 30 mA  |                  | 80   |                  | %                 |

| Frequency                               | PSM                  |                                         | I <sub>OUT</sub> ≥                                                                                                                                                                                            | 30 mA                                   |                           | 20               |      |                  | kHz               |

| Supply Current                          |                      | •                                       |                                                                                                                                                                                                               |                                         |                           | l                |      |                  |                   |

| PW                                      |                      | I <sub>SUPPLY</sub>                     |                                                                                                                                                                                                               |                                         |                           | 500              | 800  |                  |                   |

| Input Supply Current                    | PSM                  | (V <sub>DD</sub> &<br>V <sub>IN</sub> ) | $I_{OUT} = 0$ mA, $V_{IN} = 3.6$ V (not switching, FB = GND)                                                                                                                                                  |                                         |                           | 400              |      | μΑ               |                   |

| Shutdown Supply Curren                  | t                    | I <sub>SD</sub>                         | SD = Low                                                                                                                                                                                                      |                                         |                           |                  | 2    |                  |                   |

| Thermal Shutdown                        | 1                    |                                         |                                                                                                                                                                                                               |                                         |                           |                  |      |                  |                   |

| Thermal Shutdown Temp                   | erature <sup>c</sup> | T <sub>J(S/D)</sub>                     |                                                                                                                                                                                                               |                                         |                           |                  | 165  |                  |                   |

| Thermal Hysteresis <sup>c</sup>         |                      |                                         |                                                                                                                                                                                                               |                                         | 20                        |                  | °C   |                  |                   |

- Notes

a. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum, is used in this data sheet.

b. Typical values are for DESIGN AID ONLY, not guaranteed or subject to production testing.

c. Guaranteed by design.

d. Settling times, t<sub>s</sub>, apply after t<sub>en</sub>.

e. Bypass is a device mode of operation, in which, the device is in 100% duty cycle. Bypass operation is possible in either PWM or PSM.

f. Operating modes are controlled with the MODE pin where Auto mode = MODE = LOW, PWM Mode = MODE = HIGH, and PSM mode = MODE = OPEN.

#### **New Product**

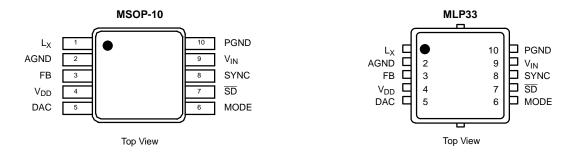

#### PIN CONFIGURATION

| PIN DESCRIPTION |                 |                                                                                                      |  |  |  |

|-----------------|-----------------|------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Number      | Name            | Function                                                                                             |  |  |  |

| 1               | L <sub>X</sub>  | Inductor connection                                                                                  |  |  |  |

| 2               | AGND            | Low power analog ground                                                                              |  |  |  |

| 3               | FB              | Output voltage feedback                                                                              |  |  |  |

| 4               | $V_{DD}$        | Input supply voltage for the analog circuit.                                                         |  |  |  |

| 5               | DAC             | Voltage from external DAC to adjust output voltage.                                                  |  |  |  |

| 6               | MODE            | Used to select switching mode of the buck converter  PWM/PSM Pin Logic:  MODE Pin Operating Mode     |  |  |  |

|                 |                 | V <sub>IN</sub> PWM Open PSM GND AUTO                                                                |  |  |  |

| 7               | SD              | Logic low disables IC and reduces quiescent current to below 2 μA                                    |  |  |  |

| 8               | SYNC            | Converter switching frequency can be synchronized to $^{1}/_{6}$ of the clock frequency at this pin. |  |  |  |

| 9               | V <sub>IN</sub> | Input supply voltage                                                                                 |  |  |  |

| 10              | PGND            | Low impedance power ground                                                                           |  |  |  |

| ORDERING I  | INFORMATION |             |             |         |             |

|-------------|-------------|-------------|-------------|---------|-------------|

|             | MSOP-10     |             |             | MLP33   |             |

| Part Number | Marking     | Temperature | Part Number | Marking | Temperature |

| Si9174DH-T1 | 9174        | -40 to 85°C | Si9174DM-T1 | 9174    | -40 to 85°C |

Additional voltage options are available.

| Eval Kit | Temperature Range | Board         |

|----------|-------------------|---------------|

| Si9174DB | -40 to 85°C       | Surface Mount |

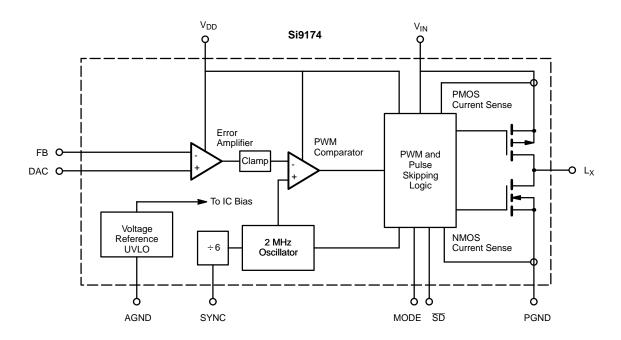

#### **FUNCTIONAL BLOCK DIAGRAM**

**New Product**

#### **DETAIL DESCRIPTION**

#### General

The Si9174 is a high efficiency synchronous dc-dc converter that is ideally suited for lithium ion battery or three cell alkaline applications, as well as step-down of 3.3-V or 5.0-V supplies. It is design to provide power to the power amplifier in WCDMA cell phones, but can utilized in any applications requiring a dynamically adjustable 600-mA power supply. The major blocks of the Si9174 are shown in the Functional Block Diagram. The  $0.25-\Omega$  internal MOSFETs switching at a frequency of 2-MHz minimize PC board space while providing high conversion efficiency and performance. The high frequency error-amplifier with built-in loop compensation minimizes external components and provides rapid output settling times of <30 µs. Sensing of the inductor current for control is accomplished internally without power wasting resistors. The switching frequency can be synchronized to an external 13-MHz clock signal.

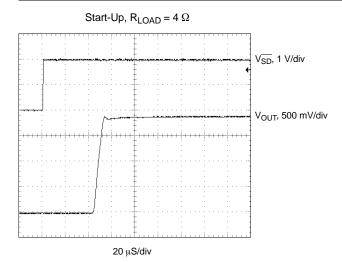

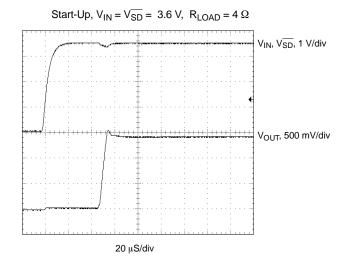

#### Start-Up

When voltage is applied to  $V_{IN}$  and  $V_{DD}$ , the under-voltage lockout (UVLO) circuit prevents the oscillator and control circuitry from turning on until the voltage on the exceeds 2.4 V. With a typical UVLO hysteresis of 0.1 V, the converter operates continuously until the voltage on  $V_{IN}$  drops below 2.3 V, whereupon the converter shuts down. This hysteresis

prevents false start-stop cycling as the input voltage approaches the UVLO switching threshold. Start-up is always accomplished in PWM mode to ensure start-up under all load conditions. Switching to other modes of operation occurs according to the state of the MODE pin and the load current. The start-up sequence occurs after  $\overline{\text{SD}}$  switches from LOW to HIGH with  $\text{V}_{\text{IN}}$  applied, or after  $\text{V}_{\text{IN}}$  rises above the UVLO threshold and  $\overline{\text{SD}}$  is a logic HIGH.

#### **Mode Control (MODE)**

The MODE pin allows the user to control the mode of operation or to enable the Si9174 to automatically optimize the mode of operation according to load current. There are three different modes of operation as controlled by the MODE pin. Switching waveforms are shown in the Typical Switching Waveform sections, page 9.

#### PWM Mode (MODE pin = HIGH)

With the MODE pin in the logic HIGH condition, the Si9174 operates as a 2-MHz fixed frequency voltage mode converter. A NMOS synchronous rectification MOSFET transistor provides very high conversion efficiency for large load currents by minimizing the conduction losses. PWM mode provides low output ripple, fast transient response, and switching frequency synchronization. Output load currents can range from 0 to 600 mA.

#### **New Product**

The error amplifier and comparator control the duty cycle of the PMOS MOSFET to continuously force the DAC pin and FB pin voltages to be equal. As the input-to-output voltage difference drops, the duty cycle of the PMOS MOSFET can reach 100% to allow system designers to extract the maximum stored energy from the battery. The dropout voltage is 190 mV at 600 mA.

During each cycle, the PMOS switch current is limited to a maximum of 1.5 A (typical) thereby protecting the IC while continuing to force maximum current into the load. Similarly, the NMOS switch is internally limited to a maximum of 1.5 A (typical) during negative output voltage transients.

#### Pulse Skipping Mode (MODE pin = OPEN)

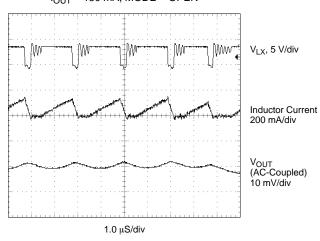

By leaving the MODE pin open-circuit, the converter runs in pulse skipping mode (PSM). In PSM mode the oscillator continues to operate, but switching only occurs if the FB pin voltage is below the DAC voltage at the start of each clock cycle. Clock cycles are skipped thereby reducing the switching frequency to well below 100 kHz and minimizing switching losses for improved efficiency at loads under 150 mA. Although PSM mode switching frequency varies with line and load conditions, the minimum PSM frequency will be kept above 20 kHz for load currents of 30 mA or more to prevent switching noise from reaching the audio frequency range.

Each time the PMOS switch is turned on, the inductor current is allowed to reach 300 mA. Once achieved, the PMOS switch is turned off and the NMOS switch is turned on in the normal manner. However, unlike PWM mode, the NMOS switch, turns off as the switch current approaches zero current to maximize efficiency. The PMOS switch remains on continuously (100% duty cycle) when the input-voltage-to-output-voltage difference is low enabling maximum possible energy extraction from the battery.

PSM mode is recommend for load currents of 150 mA or less.

#### **Auto Mode**

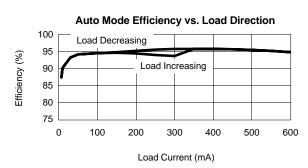

When the MODE pin grounded, the converter is set to Auto mode. Switching between PWM mode and PSM modes takes place automatically without an external control signal. For heavy load operation, the converter will operate in PWM mode to achieve maximum efficiency. When delivering light load currents, the converter operates in PSM mode to conserve power. The switchover threshold between the two modes is determined by the peak inductor current, which is 300 mA nominal. There is hysteresis in the switchover threshold to

provide smooth operation. Thus, the mode PSM-to-PWM mode switchover current for increasing load currents is higher than that of PWM-to-PSM mode switchover for decreasing load currents.

#### **Oscillator Synchronization (SYNC)**

The internal oscillator provides for a fixed 2-MHz switching frequency. In order to minimize system noise, the oscillator of the Si9174 can be synchronized to an external clock, typically an ac-coupled 13-MHz sine wave. An on-chip divide-by-six circuit sets the converter switching frequency to 2.167 MHz in this mode. The frequency lock range of the synchronization circuitry is typically 20%. If synchronization is not required, the SYNC pin must be tied to GND permitting the internal oscillator to oscillate at 2 MHz.

#### **Dynamic Output Voltage Control (DAC)**

The Si9174 is designed to dynamically adjust the output voltage according to the voltage present on the DAC pin. The output voltage is regulated to the same voltage the DAC pin through the resistor divider. For VDAC within the voltage range of 0.28 – 2.45 V, VOUT is proportional to VDAC according to the following relationship:

$$V_{OUT} = \left(1 + \frac{R_1}{R_2}\right) \times V_{DAC}$$

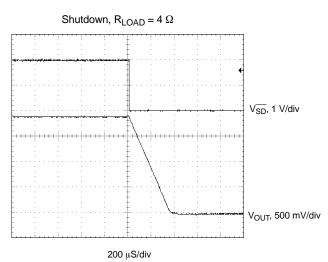

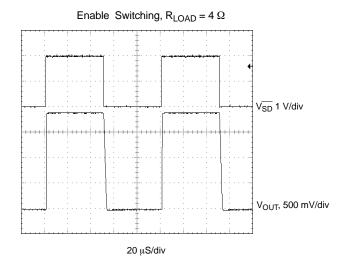

#### Converter Shutdown (SD pin)

With logic LOW level on the  $\overline{SD}$  pin, the Si9174 is shutdown. Shutdown reduces current consumption to less than 2- $\mu$ A by shutting off all of the internal circuits. Both the PMOS and NMOS transistors are turned off. A logic HIGH enables the IC to start up as described in "Start-up" section.

#### **Thermal Shutdown**

The Si9174 includes thermal shutdown circuitry, which turns off the regulator when the junction temperature exceeds 165°C. Once the junction temperature drops below 145°C, the regulator is enabled. If the condition causing the over temperature, the Si9174 begins thermal cycling, turning the regulator on and off in response to junction temperature. Restart from a thermal shutdown condition is the same as described in the "Start-up" section.

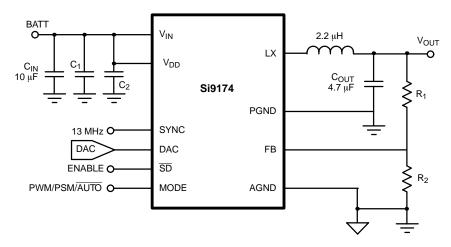

#### **APPLICATIONS CIRCUIT**

$C_{IN}$  = 10 μF, Ceramic, Murata GRM42-2X5R106K16  $C_1,\,C_2$  = 0.01 μF, Vishay VJ0603Y 104KXXAT  $C_{OUT}$  = 4.7 μF, Ceramic, Murata GRM42-6X5R475K16  $R_1$  = 8.2 kΩ, Vishay CRCW0603132F  $R_2$  = 20 kΩ, Vishay CRCW06032002F  $L_1$  = 2.2 μH, Toko A914BYW-2R2M

#### **TYPICAL CHARACTERISTICS**

**New Product**

**Figure 1.**  $V_{OUT}$ -vs.  $V_{DAC}$  Characteristics ( $V_{IN} = 5 V$ )

Figure 2. PWM Mode V<sub>OUT</sub> Settling

#### **New Product**

#### TYPICAL CHARACTERISTICS

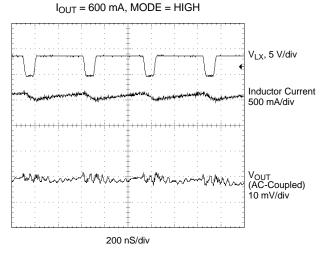

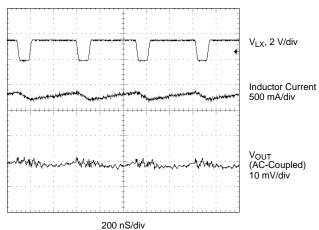

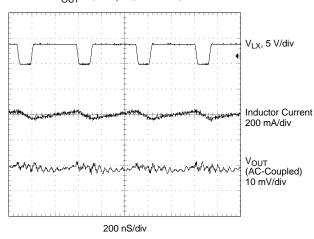

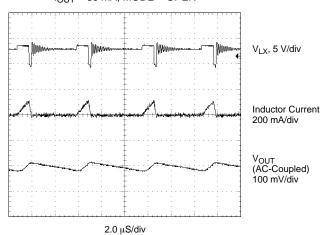

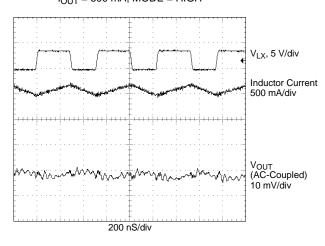

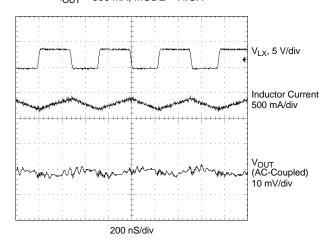

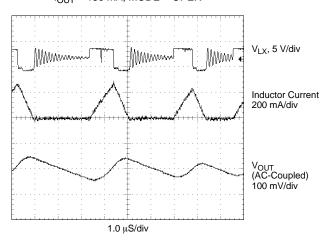

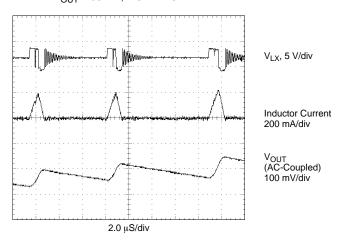

## TYPICAL SWITCHING WAVEFORMS (V<sub>IN</sub> = 3.6 V, V<sub>OUT</sub> = 3.0 V)

**New Product**

### PWM mode Heavy-Load Switching Waveforms,

### PWM Mode Medium-Load Switching Waveforms, $I_{OUT} = 300$ mA, MODE = HIGH

### PWM Mode Light-Load Switching Waveforms, $I_{OUT} = 0$ mA, MODE = HIGH

PSM Mode Light-Load Switching Waveforms,  $I_{OUT} = 150$  mA, MODE = OPEN

### PSM Mode Light-Load Switching Waveforms, $I_{OUT} = 30 \text{ mA}, \text{MODE} = \text{OPEN}$

#### **New Product**

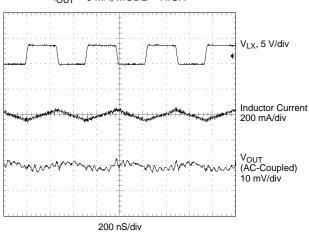

#### TYPICAL WAVEFORMS (VIN = 3.6 V, VOUT = 1.9 V)

PWM Mode Heavy-Load Switching Waveforms,  $I_{OUT} = 600 \text{ mA}, \text{MODE} = \text{HIGH}$

PWM Mode Medium-Load Switching Waveforms,  $I_{OUT} = 300 \text{ mA}$ , MODE = HIGH

PWM Mode Light-Load Switching Waveforms,  $I_{OUT} = 0$  mA, MODE = HIGH

PSM Mode Light-Load Switching Waveforms, I<sub>OUT</sub> = 150 mA, MODE = OPEN

PSM Mode Light-Load Switching Waveforms,  $I_{OUT} = 30 \text{ mA}, \text{MODE} = \text{OPEN}$

#### **New Product**

### TYPICAL START-UP AND SHUTDOWN TRANSIENT WAVEFORMS ( $V_{IN}$ = 3.6 V, $V_{OUT}$ = 1.9 V)

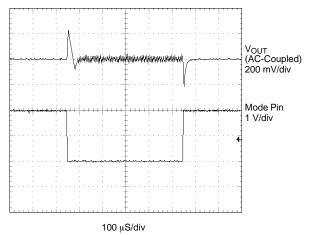

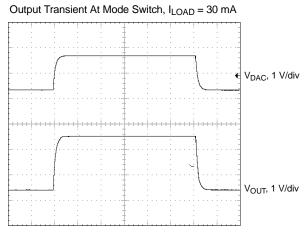

#### TYPICAL MODE SWITCH TRANSIENT WAVEFORM

#### **New Product**

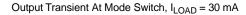

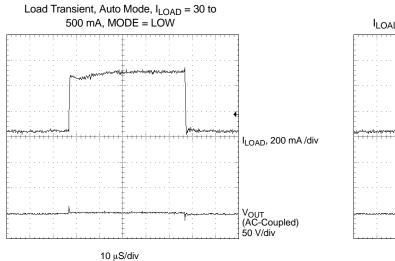

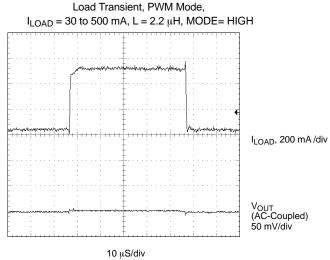

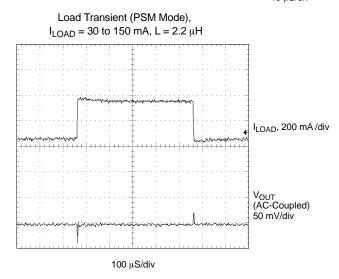

### TYPICAL LOAD TRANSIENT WAVEFORMS ( $V_{IN} = 3.6 \text{ V}, V_{OUT} = 1.9 \text{ V}$ )

#### TYPICAL DAC INPUT RESPONSE WAVEFORM

100 μS/div