INTEGRATED CIRCUITS

Preliminary specification File under Integrated Circuits, IC02 1998 Sep 03

## **TDA8354Q**

### **FEATURES**

- · Few external components

- · Highly efficient fully DC-coupled vertical output bridge circuit

- Short rise and fall times of the vertical flyback switch

- · Guard circuit

- Temperature (thermal) protection

- · High ElectroMagnetic Compatibility (EMC) because of common mode inputs

- Guard signal in zoom mode.

QUICK REFERENCE DATA

#### **GENERAL DESCRIPTION**

The TDA8354Q is a power circuit for use in 90° and 110° colour deflection systems for field frequencies of 25 to 200 Hz and 16 : 9 picture tubes. The circuit provides a DC-driven vertical deflection output circuit, operating as a highly efficient class G system. Due to the full bridge output circuit the deflection coils can be DC coupled.

The IC is constructed in a low-voltage DMOS process that combines bipolar, CMOS and DMOS devices, to provide ruggedness.

| SYMBOL                    | PARAMETER                                          | CONDITIONS  | MIN.           | TYP. | MAX. | UNIT |

|---------------------------|----------------------------------------------------|-------------|----------------|------|------|------|

| DC supply                 |                                                    |             |                |      |      |      |

| V <sub>P</sub>            | supply voltage                                     |             | 7.5            | 12   | 18   | V    |

| I <sub>q(av)</sub>        | average quiescent supply current                   | during scan | _              | 10   | 15   | mA   |

| V <sub>flb</sub>          | flyback supply voltage                             |             | $2 \times V_P$ | 45   | 68   | V    |

| I <sub>Vflb(av)</sub>     | average flyback supply current                     | during scan | _              | -    | 10   | mA   |

| Vertical circu            | iit                                                |             |                |      |      |      |

| I <sub>o(p-p)</sub>       | output current (peak-to-peak value)                |             | -              | -    | 3.2  | А    |

| I <sub>i(diff)(p-p)</sub> | input current (peak-to-peak value) at pin 11 or 12 |             | -              | 500  | 600  | μA   |

| Flyback swit              | ch                                                 |             |                |      |      |      |

| I <sub>o(Vflb)</sub>      | peak output current                                | t ≤ 1.5 ms  | -              | -    | ±1.6 | А    |

| Thermal data              | (in accordance with IEC 747-1)                     |             |                |      |      |      |

| T <sub>stg</sub>          | storage temperature                                |             | -55            | -    | +150 | °C   |

| T <sub>amb</sub>          | operating ambient temperature                      |             | -25            | -    | +75  | °C   |

| Тį                        | junction temperature                               |             | _              | _    | 150  | °C   |

### **ORDERING INFORMATION**

| ТҮРЕ     |        | PACKAGE                                                          |          |

|----------|--------|------------------------------------------------------------------|----------|

| NUMBER   | NAME   | DESCRIPTION                                                      | VERSION  |

| TDA8354Q | DBS13P | plastic DIL-bent-SIL power package; 13 leads (lead length 12 mm) | SOT141-6 |

TDA8354Q

# Full bridge current driven vertical deflection output circuit in LVDMOS

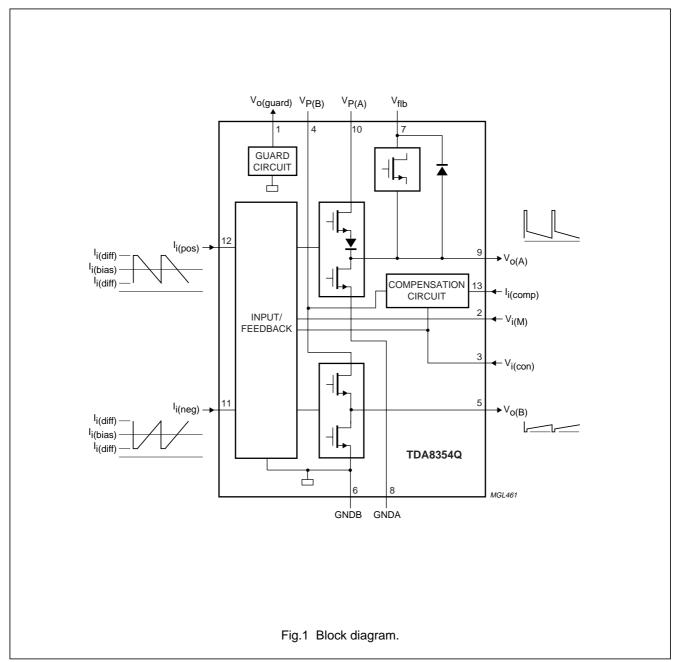

### **BLOCK DIAGRAM**

## TDA8354Q

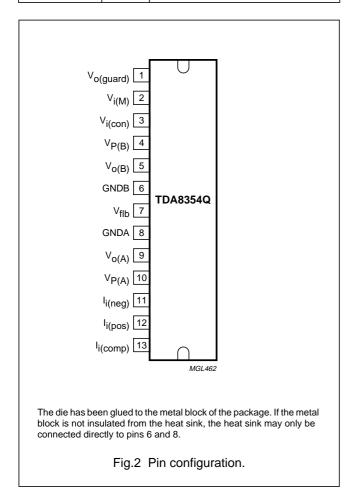

#### PINNING

| SYMBOL                | PIN | DESCRIPTION                                                                |

|-----------------------|-----|----------------------------------------------------------------------------|

| V <sub>o(guard)</sub> | 1   | guard output voltage                                                       |

| V <sub>i(M)</sub>     | 2   | measuring resistor input                                                   |

| V <sub>i(con)</sub>   | 3   | conversion resistor input                                                  |

| V <sub>P(B)</sub>     | 4   | supply voltage B                                                           |

| V <sub>o(B)</sub>     | 5   | output voltage B                                                           |

| GNDB                  | 6   | ground B                                                                   |

| V <sub>flb</sub>      | 7   | flyback supply voltage                                                     |

| GNDA                  | 8   | ground A                                                                   |

| V <sub>o(A)</sub>     | 9   | output voltage A                                                           |

| V <sub>P(A)</sub>     | 10  | supply voltage A                                                           |

| I <sub>i(neg)</sub>   | 11  | input power-stage (negative);<br>includes l <sub>i(bias)</sub> signal bias |

| l <sub>i(pos)</sub>   | 12  | input power-stage (positive);<br>includes l <sub>i(bias)</sub> signal bias |

| I <sub>i(comp)</sub>  | 13  | damping resistor compensation current input                                |

### FUNCTIONAL DESCRIPTION

The vertical driver circuit is a bridge configuration. The deflection coil is connected between the output amplifiers, which are driven in phase opposition. The differential input circuit is current driven. The input circuit is special intended for direct connection to driver circuits which deliver symmetrical current signals, but is also suitable for asymmetrical currents. The current to voltage conversion is done by the external resistor (R<sub>con</sub>) connected between the output of the input conversion stage and output stage B. This voltage is compared with the output current through the deflection coil measured as voltage across R<sub>M</sub>, which provides internal feedback information. The relationship between the differential input current and the output current is defined by:  $2 \times I_{i(diff)} \times R_{con} = I_{coil} \times R_M$  The output current is adjustable from 0.5 A (p-p) to 3.2 A (p-p) by varying R<sub>con</sub>. The maximum input current is 800 µA peak for each pin. The minimum input current should be 50  $\mu$ A.

### Flyback supply

The flyback voltage is determined by an additional supply voltage V<sub>flb</sub>. The principle of operating with two supply voltages (class G) makes it possible to fix the supply voltage V<sub>P</sub> optimum for the scan voltage and the second supply voltage V<sub>flb</sub> optimum for the flyback voltage. Using this method, very high efficiency is achieved. The supply voltage V<sub>flb</sub> is almost totally available as flyback voltage across the coil, this being possible due to the absence of a coupling capacitor (not necessary, due to the bridge configuration). The very short rise and fall time of the flyback switch is >400 V/µs.

### Protection

The output circuit has protection circuits for:

- Die temperature control

- Overvoltage of output stage A.

## TDA8354Q

### **Guard circuit**

A guard circuit with output signal  $V_{o(guard)}$  is provided.

The guard circuit generates an active HIGH level during the flyback period. The guard circuit is also activated for one or more of the following conditions:

- When the thermal protection is activated ( $T_i \approx 170 \text{ °C}$ )

- During short-circuit of the output pins (pins 5 and 9) to  $V_{\text{P}}$  or ground

- During open coil

- During open loop

- During short-circuit of the input pins (pins 11 and 12) to  $V_{\rm P}$  or ground.

An active HIGH level of the guard signal is also generated for the next conditions:

- No drive signal

- Short-circuit of the coil.

However, for these events the signal is generated via an internal timer circuit. The guard signal set via this timer has a delay of  $\approx$ 120 ms. The delay time is given by the lowest applicable field frequency.

The guard signal can be used for blanking the picture tube screen and signalling a fault condition.

#### Damping resistor compensation

For HF-loop stability a damping resistor is connected across the deflection coil. There is a big difference in current in the damping resistor  $R_p$  during scan and flyback. The resistor current is summed to the current in the deflection coil via the measuring resistor  $R_M$ , which results in a too low current in the deflection coil at the start of the scan.

To reach a short settling time the difference in the current during scan and flyback in the damping resistor can be compensated for by external means. To do so a resistor ( $R_{comp}$ ) of about 1 M $\Omega$  can be connected between the output of stage A (pin 9) and the damping resistor compensation current input (pin 13).

For a more accurate calculation of  $\mathsf{R}_{\mathsf{comp}}$  refer to the following formula:

$$R_{comp} = \frac{(V_{flb} - V_{loss} - V_{p}) \times R_{p} \times R_{con}}{(V_{flb} - V_{loss} - I_{L} \times R_{L}) \times R_{M}}$$

## TDA8354Q

### LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134).

| SYMBOL                      | PARAMETER                                          | CONDITIONS                          | MIN. | MAX.           | UNIT |

|-----------------------------|----------------------------------------------------|-------------------------------------|------|----------------|------|

| DC supply                   |                                                    | ·                                   | ŀ    |                | •    |

| VP                          | supply voltage                                     |                                     | _    | 18             | V    |

| V <sub>flb</sub>            | flyback supply voltage                             |                                     | -    | 68             | V    |

| Vertical circu              | Jit                                                | •                                   |      |                | •    |

| I <sub>o(p-p)</sub>         | output current (peak-to-peak value)                |                                     | _    | 3.2            | А    |

| V <sub>o(A)</sub>           | output voltage (pin 9)                             | note 1                              | -    | 68             | V    |

| V <sub>o(B)</sub>           | output voltage (pin 5)                             |                                     | -    | V <sub>P</sub> | V    |

| I <sub>1,2,3,11,12,13</sub> | current into or out of<br>pins 1 to 3 and 11 to 13 |                                     | -20  | +20            | mA   |

| V <sub>1,2,3,11,12,13</sub> | peak voltage on pins 1 to 3 and 11 to 13           |                                     | -0.5 | V <sub>P</sub> | V    |

| Flyback swit                | ch                                                 | ·                                   |      |                | •    |

| I <sub>o(Vflb)</sub>        | peak output current                                |                                     | -    | ±1.6           | А    |

| Thermal data                | a (in accordance with IEC 747-1)                   |                                     |      |                |      |

| T <sub>stg</sub>            | storage temperature                                |                                     | -55  | +150           | °C   |

| T <sub>amb</sub>            | operating ambient temperature                      |                                     | -25  | +75            | °C   |

| Tj                          | junction temperature                               | note 2                              | -    | 150            | °C   |

| Miscellaneou                | us                                                 |                                     |      |                |      |

| t <sub>sc</sub>             | short-circuiting time                              | note 3                              | _    | 1              | h    |

| l <sub>i/o</sub>            | current into any pin                               | +1.5 × $ V_{P(max)} $ ; note 4      | -    | +200           | mA   |

|                             | current out of any pin                             | $-1.5 \times  V_{P(max)} $ ; note 4 | -200 | _              | mA   |

| V <sub>ESD</sub>            | electrostatic handling                             | note 5                              | -    | ±300           | V    |

|                             |                                                    | note 6                              | -    | ±2000          | V    |

### Notes

1. When the pin voltage exceeds 70 V the device behaves like a power zener diode thus limiting the voltage.

- 2. Internally limited by thermal protection; switching point  $\approx$ 170 °C.

- 3. Up to  $V_P = 18 V$ .

- 4. At T<sub>j(max)</sub>.

5. Machine model: equivalent to discharge a 200 pF capacitor through a 0  $\Omega$  series resistor. Except pin 7: ±250 V.

6. Human body model: equivalent to discharge a 100 pF capacitor through a 1.5 k $\Omega$  series resistor. Except pin 7:  $\pm 1500$  V.

## TDA8354Q

## THERMAL CHARACTERISTICS

| SYMBOL               | PARAMETER                                   | CONDITIONS  | VALUE | UNIT |

|----------------------|---------------------------------------------|-------------|-------|------|

| R <sub>th(j-c)</sub> | thermal resistance from junction to case    |             | 4     | K/W  |

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient | in free air | 40    | K/W  |

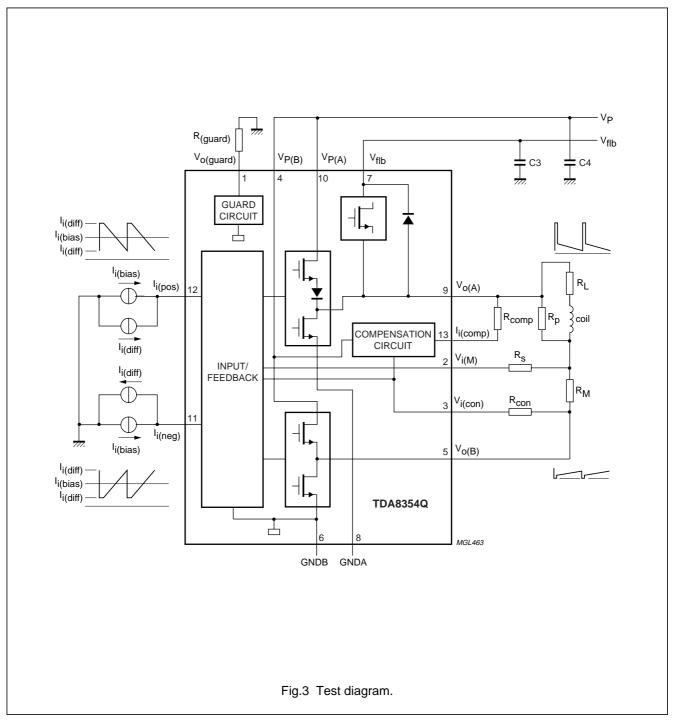

## CHARACTERISTICS

$V_P$  = 12 V;  $V_{flb}$  = 45 V;  $f_i$  = 50 Hz;  $I_{i(bias)}$  = 330  $\mu$ A;  $T_{amb}$  = 25 °C; measured in test circuit of Fig.3; unless otherwise specified.

| SYMBOL                                   | PARAMETER                                                       | CONDITIONS                                                 | MIN.           | TYP.            | MAX. | UNIT |  |

|------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------|----------------|-----------------|------|------|--|

| DC supply                                |                                                                 | •                                                          |                |                 |      |      |  |

| VP                                       | operating supply voltage                                        |                                                            | 7.5            | 12              | 18   | V    |  |

| V <sub>flb</sub>                         | flyback supply voltage                                          |                                                            | $2 \times V_P$ | 45              | 68   | V    |  |

| I <sub>q(av)</sub>                       | average quiescent supply current                                | during scan                                                | _              | 10              | 15   | mA   |  |

| lq                                       | quiescent supply current                                        | no signal; no load                                         | _              | 60              | 80   | mA   |  |

| I <sub>Vflb(av)</sub>                    | average flyback supply current                                  | during scan                                                | _              | -               | 10   | mA   |  |

| Output stag                              | e A and B                                                       | •                                                          |                |                 |      |      |  |

| V <sub>loss</sub>                        | voltage loss from pin 10 to 9 and from pin 5 to 6               | I <sub>o</sub> = 3.2 A (p-p); note 1                       | -              | -               | 6.0  | V    |  |

| -                                        | voltage loss from pin 4 to 5 and from pin 9 to 8                |                                                            | -              | -               | 4.8  | V    |  |

|                                          | voltage loss from pin 10 to 9 and from pin 5 to 6               | I <sub>o</sub> = 2.2 A (p-p); note 1                       | -              | -               | 4.2  | V    |  |

|                                          | voltage loss from pin 4 to 5 and from pin 9 to 8                |                                                            | -              | -               | 3.4  | V    |  |

| LE                                       | linearity error                                                 |                                                            |                |                 |      |      |  |

|                                          | adjacent blocks                                                 | I <sub>o</sub> = 3.2 A (p-p); note 2                       | -              | 0.5             | 2    | %    |  |

|                                          | not adjacent blocks                                             | I <sub>o</sub> = 3.2 A (p-p); note 2                       | -              | 0.5             | 3    | %    |  |

| Vo                                       | output voltage swing (flyback) $V_{o(A)} - V_{o(B)}$            | $I_{i(diff)} = 0.3 \text{ mA};$<br>$I_{o} = 1.6 \text{ A}$ | -              | 46              | -    | V    |  |

| V <sub>offset</sub>                      | offset voltage across R <sub>M</sub>                            | $I_{i(diff)} = 0$                                          |                |                 |      |      |  |

|                                          |                                                                 | $I_{i(bias)} = 500 \ \mu A$                                | -              | _               | 15   | mV   |  |

|                                          |                                                                 | l <sub>i(bias)</sub> = 100 μA                              | -              | -               | 13   | mV   |  |

| $\Delta V_{\text{offset}(T)}$            | offset voltage as function of temperature                       | $I_{i(diff)} = 0$                                          | -              | -               | 40   | μV/K |  |

| V <sub>o(A)</sub> , V <sub>o(B)</sub>    | DC output voltage                                               | $I_{i(diff)} = 0;$ note 3                                  | -              | $\frac{V_P}{2}$ | -    | V    |  |

| G <sub>v(ol)</sub>                       | open-loop voltage gain V <sub>9 to 5</sub> /V <sub>3 to 5</sub> | notes 4 and 5                                              | _              | 60              | -    | dB   |  |

| V <sub>3 to 5</sub> /V <sub>2 to 5</sub> |                                                                 | note 4                                                     | -              | 0               | -    | dB   |  |

| f <sub>res</sub>                         | frequency response (-3 dB)                                      | open loop                                                  | _              | 1               | -    | kHz  |  |

| G <sub>i</sub>                           | current gain (I <sub>o</sub> /I <sub>i(diff)</sub> )            |                                                            | _              | 8000            | _    |      |  |

## TDA8354Q

| SYMBOL                    | PARAMETER                                                            | CONDITIONS                                 | MIN. | TYP. | MAX. | UNIT |  |

|---------------------------|----------------------------------------------------------------------|--------------------------------------------|------|------|------|------|--|

| $\Delta G_{i(T)}$         | current gain drift as function of temperature                        |                                            | -    | -    | 10-4 | /K   |  |

| PSRR                      | power supply rejection ratio                                         | note 6                                     | 80   | 90   | -    | dB   |  |

| Input stage               |                                                                      |                                            |      |      |      |      |  |

| I <sub>i(bias)</sub>      | signal bias current                                                  |                                            | -    | 330  | 500  | μA   |  |

| I <sub>i(diff)(p-p)</sub> | differential mode input current<br>(peak-to-peak value) pin 11 or 12 | note 7                                     | -    | 500  | 600  | μA   |  |

| V <sub>i(diff)</sub>      | differential mode input voltage                                      | l <sub>i(diff)</sub> = 500 μA              | -    | 0.75 | _    | V    |  |

| V <sub>i(cm)</sub>        | common mode input voltage                                            | I <sub>i(bias)</sub> = 330 μA              | 0.95 | 1.15 | 1.35 | V    |  |

| Flyback sw                | itch                                                                 | •                                          |      |      |      | •    |  |

| I <sub>o(Vflb)</sub>      | output peak current                                                  | t < 1.5 ms                                 | -    | -    | ±1.6 | А    |  |

| V <sub>loss</sub>         | voltage loss (V <sub>flb</sub> – V <sub>o(A)</sub> )                 | I <sub>o</sub> = +1.6 A                    | -    | 8    | 9    | V    |  |

| Guard circu               | lit                                                                  |                                            |      |      |      |      |  |

| I <sub>o(guard)</sub>     | output current                                                       | not active;<br>V <sub>o(guard)</sub> = 0 V | -    | _    | 10   | μA   |  |

|                           |                                                                      | active; V <sub>o(guard)</sub> = 4.5 V      | 1    | -    | 2.5  | mA   |  |

| V <sub>o(guard)</sub>     | output voltage on pin 1                                              | I <sub>o(guard)</sub> = 100 μA             | 5    | 6    | 7    | V    |  |

|                           | allowable voltage on pin 1                                           | maximum leakage current = 10 $\mu$ A       | _    | -    | 18   | V    |  |

### Notes

1. At  $T_i = 125$  °C. The temperature coefficient of V<sub>loss</sub> has a positive sign.

2. The linearity error is measured without S correction and based on the same measurement principle as performed on the screen. The measuring method is as follows:

Divide the output signal into 22 equal time parts ranging from 1 to 22 inclusive. Measure the value of the voltage across  $R_M$  of two succeeding parts called one block (a) starting with part 2 and 3 (block 1) and ending with part 20 and 21 (block 10). Thus parts 1 and 22 are unused. The equations for linearity error for adjacent blocks (LEAB) and not adjacent blocks (LENAB) are given below:

$$LEAB = \frac{a_k - a_{(k+1)}}{a_{av}}$$

$$LENAB = \frac{a_{max} - a_{min}}{a_{av}}$$

3.  $V_{o(A)} + V_{o(B)} = V_P$ . At the start of the scan this equation is one diode voltage less.

- 4. The V value within formulae relates to voltages at or between relative pin numbers, i.e.  $V_{9 \text{ to } 5}/V_{3 \text{ to } 5}$  = voltage value across pins 9 and 5 divided by voltage value across pins 3 and 5.

- 5.  $V_{2 to 5}$  AC short-circuited.

- 6. At  $V_{(ripple)} = 500 \text{ mV}$  (eff) at  $V_P$ ; measured across  $R_M$ ;  $f_{(ripple)} = 50 \text{ Hz} 1 \text{ kHz}$ .

- 7.  $I_{i(bias)} + I_{i(diff)} \le 800 \ \mu A \ and \ I_{i(bias)} I_{i(diff)} \ge 50 \ \mu A \ per \ pin.$

## TDA8354Q

### INTERNAL CIRCUITRY

Table 1

Equivalent pin circuits

| PIN | SYMBOL                | EQUIVALENT CIRCUIT                                                       |

|-----|-----------------------|--------------------------------------------------------------------------|

| 1   | V <sub>o(guard)</sub> |                                                                          |

| 2   | V <sub>i(M)</sub>     |                                                                          |

| 3   | V <sub>i(con)</sub>   |                                                                          |

| 4   | V <sub>P(B)</sub>     | (4)                                                                      |

| 5   | V <sub>o(B)</sub>     |                                                                          |

| 6   | GNDB                  | (5)<br>(6)<br>(6)<br>(6)<br>(6)<br>(6)<br>(6)<br>(6)<br>(6)<br>(6)<br>(6 |

## EQUIVALENT CIRCUIT PIN SYMBOL 7 $\mathsf{V}_{\mathsf{flb}}$ (10) GNDA 8 9 V<sub>o(A)</sub> 10 V<sub>P(A)</sub> (9) (8) (7)MGL471 11 I<sub>i(neg)</sub> <u>300 Ω</u> (11) Т MGL470 12 I<sub>i(pos)</sub> <u>300 Ω</u> (12) Ь MGL469 13 I<sub>i(comp)</sub> <u>300 Ω</u> (13) Г MGL468

## TDA8354Q

### **TEST AND APPLICATION INFORMATION**

TDA8354Q

## Full bridge current driven vertical deflection output circuit in LVDMOS

#### ٧P 77 R<sub>(guard)</sub> V<sub>flb</sub> + + C3 V<sub>P(A)</sub> C1 C4 C2 Vo(guard) VP(B) V<sub>flb</sub> 4 10 7 C5 GUARD CIRCUIT ٦Ь ╘ li(diff) li(bias) li(diff) li(pos) V<sub>o(A)</sub> 12 9 R<sub>comp</sub> Rp coil COMPENSATION li(comp) 13 CIRCUIT Rs DEFLECTION V<sub>i(M)</sub> 2 PROCESSOR INPUT/ FEEDBACK RM R<sub>con</sub> Vi(con) 3 li(neg) 11 V<sub>o(B)</sub> 5 li(diff) li(bias) li(diff) TDA8354Q L MGL464 GNDB GNDA $R_M = 0.5 \Omega;$ Coil: AT6216/42; $C1 = 47 \ \mu F; 100 \ V;$ $V_P = 12.1 \text{ V}$ at $f_v = 50 \text{ Hz}$ (vertical frame frequency); inclusive spread (absolute) and $R_{con} = R_s = 1.2 \text{ k}\Omega;$ C2 = 220 µF; 25 V; temperature rise in the coil; R<sub>p</sub> = 300 Ω; C3 = C4 = 100 nF; $R_{comp} = 650 \text{ k}\Omega;$ C5 = 10 nF;C6 = C7 = 10 nF. $V_{P} = 12.8 \text{ V}$ at $f_{v} = 100 \text{ Hz}$ (vertical frame frequency); inclusive spread (absolute) and temperature rise in the coil; $R_{(guard)} = 5 k\Omega.$ $$\begin{split} I_{o(p-p)} &= 2.33 \text{ A (peak-to-peak);} \\ I_{i(bias)} &= 330 \, \mu\text{A;} \\ \end{split}$$ $I_{i(diff)(12\text{-}11)} = 485 \ \mu\text{A}$ (peak value); $V_{flb} = 45 \ \text{V};$ $t_{flb} = 0.6 \text{ ms}.$ Fig.4 Application diagram.

### 1998 Sep 03

### PACKAGE OUTLINE

| S13P:              | plas         | stic C                       | DIL-be         | ent-S        | IL po            | wer          | pack           | S13P: plastic DIL-bent-SIL power package; 13 leads (lead length 12 mm) |               |                |                        |                                      |            |              |                |     |            |       |      |      | DT14             |

|--------------------|--------------|------------------------------|----------------|--------------|------------------|--------------|----------------|------------------------------------------------------------------------|---------------|----------------|------------------------|--------------------------------------|------------|--------------|----------------|-----|------------|-------|------|------|------------------|

|                    |              |                              |                |              | D                |              |                |                                                                        |               |                |                        | non-co<br>□<br>↓<br>E <sub>h</sub> — |            |              |                |     |            |       |      |      |                  |

| -                  |              |                              |                | _   `        | d                |              |                |                                                                        | <b>↓</b><br>j |                |                        |                                      |            |              |                |     |            | v (M) |      |      |                  |

| IMENSI             | IONS (       | mm ai                        | re the c       | origina      | l dime           | nsions       | .)             |                                                                        | 0             | 5<br>l<br>sca  |                        | 10 m<br>                             | m          |              |                |     |            |       |      |      |                  |

| UNIT               | A            | A <sub>2</sub>               | b <sub>p</sub> | c            | D <sup>(1)</sup> | d            | D <sub>h</sub> | E <sup>(1)</sup>                                                       | е             | e <sub>1</sub> | e <sub>2</sub>         | E <sub>h</sub>                       | j          | L            | L <sub>3</sub> | m   | Q          | v     | w    | x    | Z <sup>(1)</sup> |

| mm                 | 17.0<br>15.5 | 4.6<br>4.2                   | 0.75<br>0.60   | 0.48<br>0.38 | 24.0<br>23.6     | 20.0<br>19.6 | 10             | 12.2<br>11.8                                                           | 3.4           | 1.7            | 5.08                   | 6                                    | 3.4<br>3.1 | 12.4<br>11.0 | 2.4<br>1.6     | 4.3 | 2.1<br>1.8 | 0.8   | 0.25 | 0.03 | 2.00<br>1.45     |

|                    |              |                              | trusion        | s of 0.2     | 5 mm             | maxim        | um pei         | r side ar<br>REFE                                                      |               |                | ed.                    |                                      |            | ]            |                | EUR | OPEA       | N     |      |      |                  |

| OUTLINE<br>VERSION |              | REFERENCES<br>IEC JEDEC EIAJ |                |              |                  |              |                |                                                                        |               |                | EUROPEAN<br>PROJECTION |                                      |            | ISSUE DATE   |                |     |            |       |      |      |                  |

| OU<br>VE           | RSION        | 1                            |                | IEC          |                  |              | JEDE           | EC                                                                     |               | EIA            | ٩J                     |                                      |            |              |                | PRO | JECTIO     | ON    | 133  |      | IE               |

## TDA8354Q