# YAMAHA L S I

**YAC520** HGVC1

High Grade Volume Control

#### Outline

YAC520(HGVC1) is a high grade stereophonic digital volume for high end audio system.

It provides wide dynamic range and low distortion as well, and can control individual channels in 256 steps with 0.5 dB per step. The use of 16 bit serial data interface allows daisy chain connection of several devices for multi channel system.

Zero Crossing Detection function suppresses audible noise at quick change of the volume.

YAC520 operates on a single 5 volt power supply, and it is possible to input signal of up to 7.9Vrms by using three types of connection methods.

Development evaluation board, DMB-HGVC1, equipped with PC interface is available.

# Features

| • Wide volume range                    | A: +32.0 to - 95.0dB       | IN1=IN2          | (Input < 2.0Vrms @VDD=5V) |

|----------------------------------------|----------------------------|------------------|---------------------------|

| (can be used in three ways)            | B: +29.5 to - 97.5dB       | IN2=GND          | (Input < 2.6Vrms @VDD=5V) |

|                                        | C: +20.0 to -107.0dB       | IN1=GND          | (Input < 7.9Vrms @VDD=5V) |

| <ul> <li>Adjustment step</li> </ul>    | adjustable in 256 step     | os, with 0.5dB p | per step                  |

| ● Gain Error                           | $\pm 0.1 dB$               |                  |                           |

| ullet Low distortion factor            | 0.001% (input=150 m        | Vrms, gain=+16   | 3dB)                      |

| <ul> <li>Low residual noise</li> </ul> | $1 \mu Vrms(gain=-\infty)$ |                  |                           |

### Others

| Process               | CMOS process       |

|-----------------------|--------------------|

| Package               | 20 SSOP (YAC520-E) |

| Power supply voltage  | 5 V                |

| Operating temperature | 0 to +70 °C        |

| Load current          | 20 mA @VDD=5.0 V   |

YAMAHA CORPORATION

| YAC520 CATALOG            |  |  |  |  |

|---------------------------|--|--|--|--|

| CATALOG No.: LSI-4AC520A0 |  |  |  |  |

| 2001.3                    |  |  |  |  |

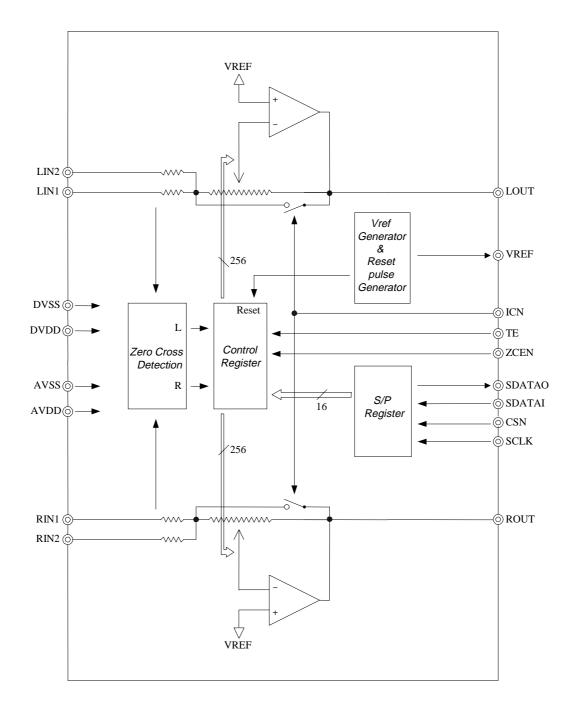

# Block Diagram

# ■ Pin Assignment

**YAC520**

Top View

# YAMAHA

# ■ Pin Functions

| AVSS – A<br>DVDD – I                                                                                                       | Analog power supply (+5.0 V)<br>Analog ground<br>Digital power supply (+5.0 V)<br>Digital ground                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Lch analog input pin<br>Gain setting range<br>gain setting range                                                           | es from +32 dB to - 95 dB when the signal inputted to LIN2 is inputted this pin, and<br>es from +20.0 dB to - 107.0 dB when it is grounded through a capacitor.                                                                      |

| Lch analog input pin<br>Gain setting range<br>gain setting range                                                           | Left Channel Analog input 2<br>o 2<br>es from +32 dB to - 95 dB when the signal inputted to LIN1 is inputted this pin, and<br>es from +29.5 dB to - 97.5 dB when it is grounded through a capacitor.<br>Right Channel Analog input 1 |

| Rch analog input pir<br>Gain setting range<br>gain setting range                                                           |                                                                                                                                                                                                                                      |

| Rch analog input pir<br>Gain setting range<br>gain setting range<br>LOUT – I<br>Lch analog output p                        | n 2<br>es from +32 dB to - 95 dB when the signal inputted to RIN1 is inputted this pin, and<br>es from +29.5 dB to - 97.5 dB when it is grounded through a capacitor.<br>Left Channel Analog output<br>in                            |

| Note this is an inv<br><b>ROUT</b> – H<br>Rch analog output p<br>Note this is an inv                                       | Right Channel Analog output<br>vin                                                                                                                                                                                                   |

| Analog reference vo                                                                                                        | Analog Reference Voltage (output)<br>oltage output pin<br>Ground through a capacitor of 10 μF or more to attain stabilization.                                                                                                       |

| Serial data input pi<br>SDATAO – S<br>Serial data putput p                                                                 | Serial Data Output                                                                                                                                                                                                                   |

| SCLK – S<br>Serial clock input p                                                                                           | Serial Clock (Input)                                                                                                                                                                                                                 |

| Chip select input pi<br>ICN – I<br>DC bias initializatio<br>To stabilize the bi<br>capacitor that is ca<br>(Refer to "VREF |                                                                                                                                                                                                                                      |

| Zero crossing cont<br>after detecting zer<br>The volume chang                                                              | rol pin. Making this pin "high" enables a mode where volume change is performed                                                                                                                                                      |

**YAC520**

ТЕ – Test Enable (Input)

Test mode control pin. Fix it to "low" or with NC when using.

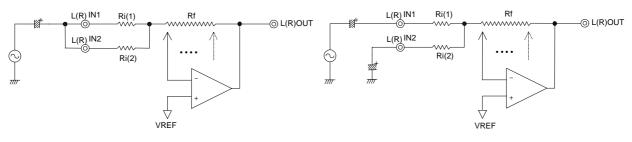

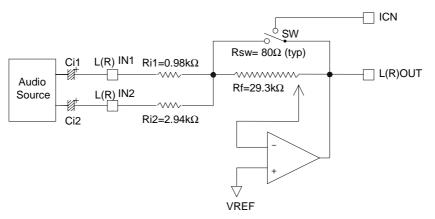

#### Description of analog functions

#### • Maximum input voltage

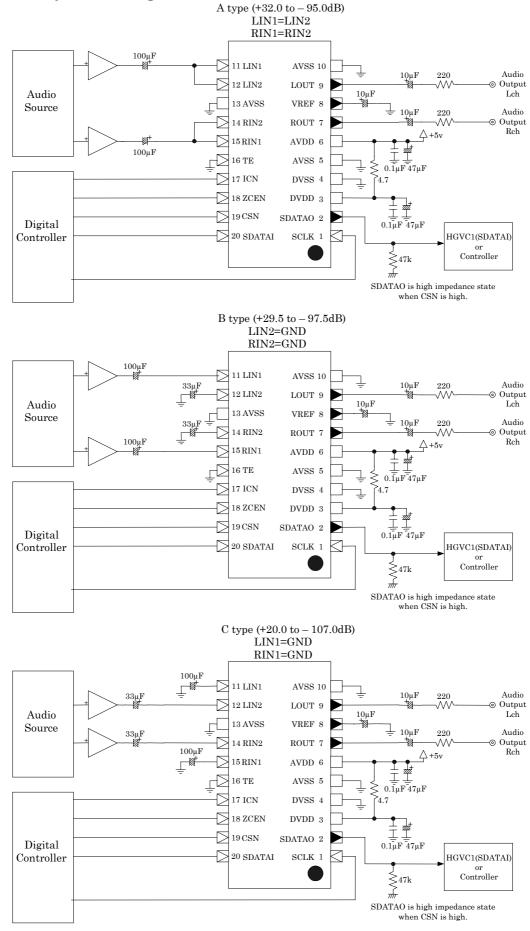

As described in the following figure, the maximum amplitude of signal that can be inputted varies according the method of the use of L(R) IN1 and 2 pins. The method A makes the maximum amplitude of the input signal approximately 2 Vrms, the method B makes it approximately 2.6 Vrms, and the method C makes it approximately 7.9 Vrms. The use of the method B or C allows to input signal exceeding the power supply voltage.

Note that the gain setting range for the method B is reduced by 2.5 dB from the one for the method A, and 12 dB for the method C.

MethodA: IN1=IN2 Gain range (+32 dB to -95 dB) Maximum input voltage: 2 Vrms

MethodB: IN2=GND Gain range (+29.5 dB to –97.5 dB) Maximum input voltage: 2.6 Vrms

MethodC: IN1=GND Gain range (+20 dB to -107 dB) Maximum input voltage: 7.9 Vrms

• VREF (analog reference voltage) stabilization time and DC bias initialization time

The time required for stabilization of VREF pin voltage after power on moment varies according to the capacitance of the capacitor connected to VREF pin. Connecting a capacitor of 10  $\mu$ F makes the time constant 30 ms (typ.). Note that the serial interface becomes invalid in this period, t<sub>PUP</sub>. As shown in the following figure, making ICN terminal "low" sets the DC bias forcibly with SW in the

LSI.

Since the time constant of L(R) IN1 and 2 pins becomes approximately 300 ms (typ.) when a capacitor of 100  $\mu F$  is used as the coupling capacitors (Ci1, 2), control ICN according to the capacitor that is connected.

Gain setting after power on =  $-\infty$

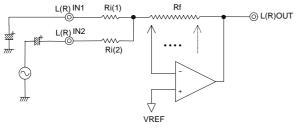

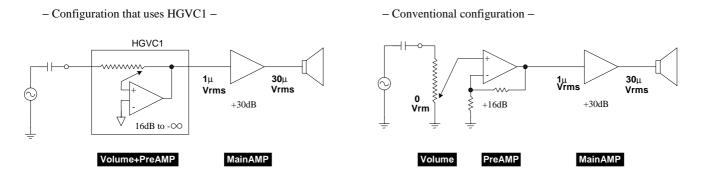

#### ■ Realization of system with low residual noise

General audio amplifiers are designed with the input sensitivity of approximately 150mV, and has gain of approximately 16 dB at PreAMP section, and approximately 30 dB at Power AMP section.

For passive volume, they are given configuration of "Volume"–"PreAMP"–"MainAMP" as shown in the above right figure. System with very small residual noise can be made by giving HGVC1 also the function of "PreAMP" because HGVC1 has the positive side gain (max : 32 dB).

Since the residual noise of HGVC1 (gain=- $\infty$ ) is 1 µVrms(typ.), the noise level at the speaker end becomes 30 µVrms if the noise of MainAMP is neglected. On the other hand, when conventional configuration is used, the noise at the speaker end becomes very large because the noise produced by the initial stage of PreAMP is amplified approximately by 46 dB (200 times) even if the level of noise produced by the volume section during mute is zero.

To achieve the noise level at the speaker end that is equivalent to the one obtained with configuration using HGVC1, the level of the noise converted to that of input of PreAMP is required to be approximately 0.16  $\mu$ Vrms (-136 dBV), which is very difficult to achieve.

As described above, HGVC1 provides advantage of making the residual noise very small because it has built-in amplifiers.

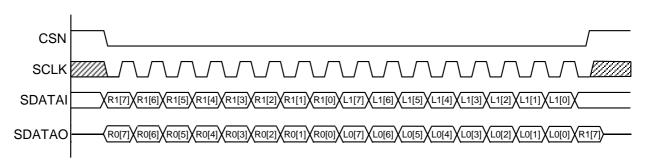

# Description of digital functions

#### Serial data interface

HGVC1 is a simple three wire serial interface. SDATAI is a serial data input pin, SCLK is a serial clock pin, and CSN is a chip select pin for writing volume value. 16 bit serial data is so formatted that SDATAI is inputted in synchronous with rise edge of SCLK when CSN is "low". (MSB first) Data is latched with the rise edge of CSN, and volume values of both left channel and right channel are set into the register. Serial data is outputted from SDATAO in synchronous with fall edge of SCLK. This data allows control by using daisy chain connection or confirmation of present volume value easily.

Note that the register value after power on is 0000h (muted state), and thus, the interface becomes valid after the time  $t_{PUP}$  elapses.

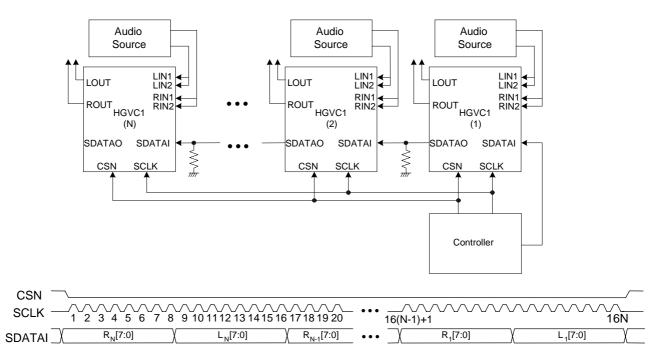

• Daisy Chaining

Since HGVC1 adopts multi channel system, multiple devices can be connected with daisy chain connection. When using the LSI in multi channel system, connection of the first SDATAO pin to the second SDATAI pin, and the second SDATAO pin to the third SDATAI pin allows control of multiple HGVC1s without requiring complex addressing. Volume data is inputted into the S/P(Serial/Parallel) register of the individual HGVC1 by holding CSN "low" for 16 clocks \* N (N represents the number of HGVCs in the chain).

(As the volume data inputted to the SDATAI of HGVC1(1) is shifted in the internal S/P register by 1 bit per SCLK clock, 16 \* N clocks are required to input volume data into S/P registers of all HGVC1(1) to HGVC1(N). Note that the first 16-bit data is inputted to the S/P register of the HGVC1(N).)

Finally, by setting CSN "High" after 16 clocks \* N period, all data in the S/P registers are written into the Control registers simultaneously to activate new volume data of all HGVC1s in the daisy chain.

#### Volume Setting

In zero crossing mode (ZCEN=H), the volume value is changed when one zero crossing is detected after the rise of CSN. The volume value is changed also when no zero crossing is detected for 20 ms. In normal mode (ZCEN=L), zero crossing detection is not performed and volume value is changed immediately after the rise of CSN.

| Input Code           | L(R)IN1=L(R)IN2          | L(R)IN2=GND              | L(R)IN1=GND              |

|----------------------|--------------------------|--------------------------|--------------------------|

| (Left/Right Channel) | Gain or Attenuation (dB) | Gain or Attenuation (dB) | Gain or Attenuation (dB) |

| 11111111             | +32.0                    | +29.5                    | +20.0                    |

| 11111110             | +31.5                    | +29.0                    | +19.5                    |

| •                    | •                        | •                        | •                        |

| •                    | •                        | •                        | •                        |

| 11010111             | +12.0                    | +9.5                     | 0                        |

| •                    | •                        | •                        | •                        |

| 11000100             | +2.5                     | 0                        | -9.5                     |

| •                    | •                        | •                        | •                        |

| 10111111             | 0                        | -2.5                     | -12.0                    |

| •                    | •                        | •                        | •                        |

| •                    | •                        | •                        | •                        |

| 00000010             | -94.5                    | -97.0                    | -106.5                   |

| 00000001             | -95.0                    | -97.5                    | -107.0                   |

| 0000000              | MUTE                     | MUTE                     | MUTE                     |

The input codes and volumes values are related as described in the following table.

#### • MUTE

Writing 0000h into register enables mute. The time mute is enabled varies between zero crossing mode (ZCEN=H) and normal mode (ZCEN=L) as described above.

# ■ Electrical Characteristics

#### • Absolute maximum ratings

| Parameter                                                                                       | Symbol | min.  | max.              | Unit |

|-------------------------------------------------------------------------------------------------|--------|-------|-------------------|------|

| Analog Supply Voltage                                                                           | AVdd   | - 0.3 | 7.0               | V    |

| Digital Supply Voltage                                                                          | DVdd   | - 0.3 | 7.0               | V    |

| Analog Input Voltage(LIN1=LIN2, RIN1=RIN2)@AVDD=DVDD=5V(LIN2=GND, RIN2=GND)(LIN1=GND, RIN1=GND) | VINA   |       | 2.0<br>2.6<br>7.9 | Vrms |

| Digital Input Voltage                                                                           | VIND   | - 0.3 | DVDD+0.3          | V    |

| Storage Temperature                                                                             | Tstg   | - 50  | 125               | °C   |

Note) DVSS = AVSS = 0V

## • Recommended operating conditions

| Parameter                     | Symbol | min. | typ. | max. | Unit |

|-------------------------------|--------|------|------|------|------|

| Analog Operating Voltage      | AVdd   | 4.75 | 5.00 | 5.25 | V    |

| Digital Operating Voltage     | DVdd   | 4.75 | 5.00 | 5.25 | V    |

| Operating Ambient Temperature | Тор    | 0    | 25   | 70   | °C   |

#### • Electrical characteristics under recommended operating conditions

• Analog Characteristics

| Parameter                                                                                  | Symbol                     | min.                        | typ.  | max.                       | Unit  |

|--------------------------------------------------------------------------------------------|----------------------------|-----------------------------|-------|----------------------------|-------|

| Gain Range (A: LIN1=LIN2, RIN1=RIN2)<br>(B: LIN2=GND, RIN2=GND)<br>(C: LIN1=GND, RIN1=GND) | Gain A<br>Gain B<br>Gain C | - 95.0<br>- 97.5<br>- 107.0 | _     | + 32.0<br>+ 29.5<br>+ 20.0 | dB    |

| Step Size                                                                                  |                            | _                           | 0.5   | -                          | dB    |

| Gain Error                                                                                 |                            | Ι                           | ± 0.1 | -                          | dB    |

| Gain Matching Between Channel (1kHz)                                                       |                            | -                           | ± 0.1 | -                          | dB    |

| Input Resistance                                                                           | Rı                         | 0.6                         | _     | 40                         | kΩ    |

| Input Capacitance                                                                          | Сі                         | Ι                           | _     | 15                         | pF    |

| Load Capacitance                                                                           | CL                         | Ι                           | _     | 100                        | pF    |

| Output Impedance                                                                           | Ro                         | -                           | 50    | -                          | Ω     |

| Signal to Noise Ratio<br>(input=150mVrms, gain=+16dB)                                      | SN                         | _                           | 100   |                            | dB    |

| Total Harmonic Distortion<br>(input=150mVrms, gain=+16dB)                                  | THD                        | _                           | 0.001 |                            | %     |

| Residual Output Noise (- $\infty$ , IHF-A)                                                 | Vn                         |                             | 1     | 2                          | μVrms |

| Inter channel Isolation (1kHz)                                                             |                            |                             | - 110 |                            | dB    |

# YAMAHA

#### • Power Supply

| Parameter                        | Symbol         | min. | Тур. | max. | Unit |

|----------------------------------|----------------|------|------|------|------|

| Power Consumption (AVDD,DVDD=5V) | P <sub>D</sub> | -    | 100  | -    | mW   |

#### • Digital DC Characteristics

| Parameter                            | Symbol | min.    | typ. | max.    | Unit |

|--------------------------------------|--------|---------|------|---------|------|

| High-Level Input voltage             | Vін    | 0.7xVdd | -    | -       | V    |

| Low-Level Input voltage              | VIL    | -       | -    | 0.3xVdd | V    |

| High-Level Output voltage(Io=-0.2mA) | Vон    | Vdd-1   | -    | -       | V    |

| Low-Level Output voltage(Io=2mA)     | Vol    | -       | -    | 0.4     | V    |

| Input Leakage Current                | ILI    | -       | -    | 10      | μΑ   |

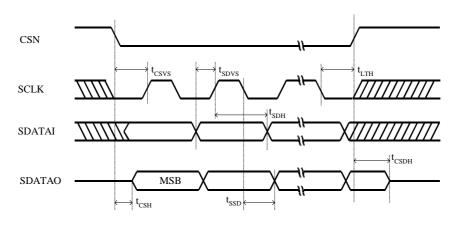

### • Digital AC Characteristics

| Parameter                              | Symbol        | min. | typ. | max. | Unit |

|----------------------------------------|---------------|------|------|------|------|

| Serial Clock                           | SCLK          | -    | -    | 6.25 | MHz  |

| Serial Clock Pulse Width High          | tрн           | 80   | -    | -    | ns   |

| Serial Clock Pulse Width Low           | tPL           | 80   | -    | -    | ns   |

| SDATAI Set Up Time                     | tsdvs         | 20   | -    | -    | ns   |

| SDATAI Hold Time                       | tSDH          | 20   | -    | -    | ns   |

| CSN Valid to SCLK Rising               | tcsvs         | 30   | -    | -    | ns   |

| SCLK Falling to CSN High               | t∟⊤н          | 35   | -    | -    | ns   |

| CSN low to Output Active (CI=20 pF)    | tcsн          | -    | -    | 35   | ns   |

| SCLK Falling to Data Valid (CI=20 pF)  | tssd          | -    | -    | 60   | ns   |

| CSN High to SDATAO Inactive            | <b>t</b> CSDH | -    | -    | 100  | ns   |

| Power-up to SPI Operation (Cvref=10µF) | tpup          | -    | 30   | 50   | ms   |

Serial Port Timing Diagram

# YAC520

## Example of System Configuration

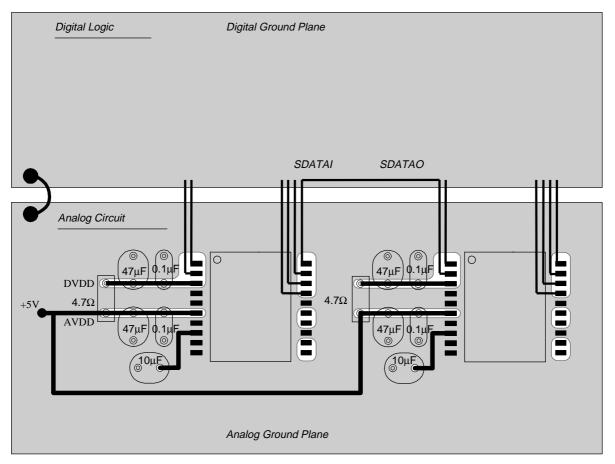

# Example of PCB Layout

To achieve the maximum performance of this device, it is necessary to take special care for the power supply and the method of grounding. (The above figure shows an example of the layout on the PCB that assumes the daisy chain connection of two HGVC1s.) Connect a regulated low noise 5 V power supply to AVDD, and de-couple with DVDD through a resistor for the purpose of avoiding mixing of noise that is generated in the serial interface. (Refer to  $\blacksquare$  Example of System Configuration) At this time, the decoupling capacitor should be located as close as possible to HGVC1. The analog domain and digital domain should be grounded separately, and HGVC1 should be located in the analog domain side, so that a pattern layout with minimized impedance to AVSS and DVSS pins can be achieved. The analog ground and digital ground should be given sufficiently wide areas respectively so that the radiation of the noise can be suppressed effectively.

Control signals such as serial interface should be placed collectively in the area nearer to the digital ground plane (upper side), and analog signals and digital signals should be arranged without crossing each other and without running side by side to prevent their interference.

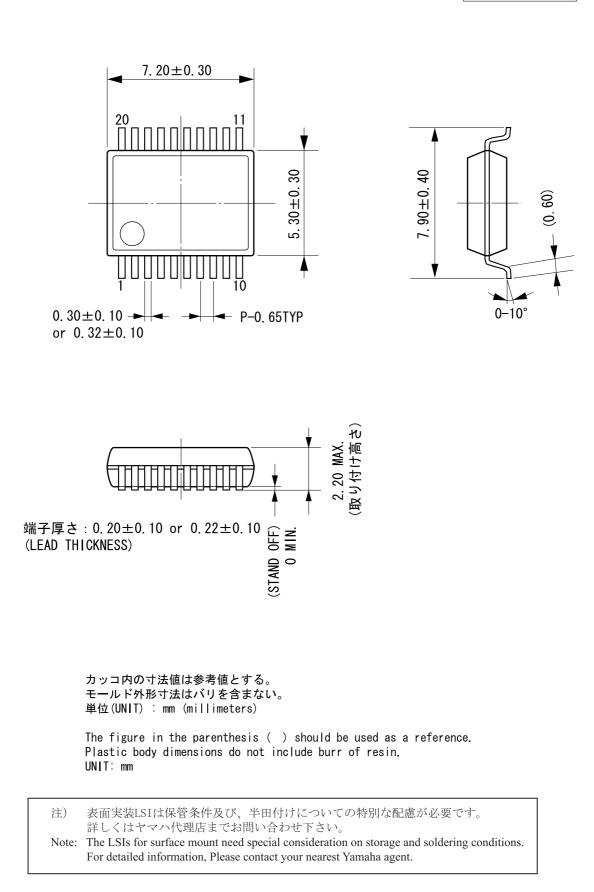

#### External Dimensions of Package

# MEMO

# **IMPORTANT NOTICE**

1. Yamaha reserves the right to make changes to its Products and to this document without notice. The information contained in this document has been carefully checked and is believed to be reliable. However, Yamaha assumes no responsibilities for inaccuracies and makes no commitment to update or to keep current the information contained in this document.

2. These Yamaha Products are designed only for commercial and normal industrial applications, and are not suitable for other uses, such as medical life support equipment, nuclear facilities, critical care equipment or any other application the failure of which could lead to death, personal injury or environmental or property damage. Use of the Products in any such application is at the customer's sole risk and expense.

3. YAMAHA ASSUMES NO LIABILITY FOR INCIDENTAL, CONSEQUENTIAL, OR SPECIAL DAMAGES OR INJURY THAT MAY RESULT FROM MISAPPLICATION OR IMPROPER USE OR OPERATION OF THE PRODUCTS.

4. YAMAHA MAKES NO WARRANTY OR REPRESENTATION THAT THE PRODUCTS ARE SUBJECT TO INTELLECTUAL PROPERTY LICENSE FROM YAMAHA OR ANY THIRD PARTY, AND YAMAHA MAKES NO WARRANTY OR REPRESENTATION OF NON-INFRANGIMENT WITH RESPECT TO THE PRODUCTS. YAMAHA SPECIALLY EXCLUDES ANY LIABILITY TO THE CUSTOMER OR ANY THIRD PARTY ARISING FROM OR RELATED TO THE PRODUCTS' INFRINGEMENT OF ANY THIRD PARTY'S INTELLECTUAL PROPERTY RIGHTS, INCLUDING THE PATENT, COPYRIGHT, TRADEMARK OR TRADE SECRET RIGHTS OF ANY THIRD PARTY.

5. EXAMPLES OF USE DESCRIBED HEREIN ARE MERELY TO INDICATE THE CHARACTERISTICS AND PERFORMANCE OF YAMAHA PRODUCTS. YAMAHA ASSUMES NO RESPONSIBILITY FOR ANY INTELLECTUAL PROPERTY CLAIMS OR OTHER PROBLEMS THAT MAY RESULT FROM APPLICATIONS BASED ON THE EXAMPLES DESCRIBED HEREIN. YAMAHA MAKES NO WARRANTY WITH RESPECT TO THE PRODUCTS, EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR USE AND TITLE.

Notice

The specification given here are provisional and subject to change without prior notice. Please confirm the latest documentation before using this product.

|        |                                          | IAHA CORPORATION ———                                                                                                                            |

|--------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| AGENCY |                                          |                                                                                                                                                 |

|        | Address inquiries t<br>Semiconductor Sal | to:<br>les & Marketing Department                                                                                                               |

|        | ■ Head Office                            | 203, Matsunokijima, Toyooka-mura<br>Iwata-gun, Shizuoka-ken, 438-0192<br>Tel. +81-539-62-4918 Fax. +81-539-62-5054                              |

|        | ■Tokyo Office                            | 2-17-11, Takanawa, Minato-ku,<br>Tokyo, 108-8568<br>Tel. +81-3-5488-5431 Fax. +81-3-5488-5088                                                   |

|        | ■Osaka Office                            | Namba Tsujimoto Nissei Bldg., 4F<br>1-13-17, Namba Naka, Naniwa-ku,<br>Osaka City, Osaka, 556-0011<br>Tel. +81-6-6633-3690 Fax. +81-6-6633-3691 |

|        |                                          |                                                                                                                                                 |